- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I've an issue similar to this post https://community.infineon.com/t5/Wi-Fi-Combo/STM32F769NI-Murata-SN8000-Problem-with-high-throughput...

I succeed to communicate through SDIO with the module, flash the module without any error but I've the error

/* If your system times out here, it means that the WLAN firmware is not booting.

* Check that your WLAN chip matches the 'wifi_image.c' being built - in GNU toolchain, $(CHIP)

* makefile variable must be correct.

*/

WPRINT_WWD_ERROR(("Timeout while waiting for high throughput clock\n"));

/*@-unreachable@*/ /* Reachable after hitting assert */

return WWD_TIMEOUT;

/*@+unreachable@*/The value of the register SDIO_CHIP_CLOCK_CSR is 0x64. One time out of 20 it's working and I've the result 0xC0. (Bit 0x80 is set).

With STM32 Connectivity pack, it's working every times. I can't use STM32 Connectivity pack because I need Wi-Fi Direct (P2P)

I used the STM32 to output the clock for LPO. This clock is always on at frequency 32.768kHz.

The SDIO clock frequency is both 5MHz with WICED and with STM32 Connectivity pack.

I downloaded WICED parameters files from Laird and adapt it to my board. (wifi_nvram_image.h, platform.c/h, platform_config.h). I tested the same set of parameters (wifi_nvram_image.h, binaries files) with STM32 Connectivity pack and it's working.

I check every signals with oscilloscope and I didn't see any major differences.

I use WICED 6.2 because STM32H753 MCU is already added. I adapted files for STM32H733.

Do you have any solutions?

Thank you

Solved! Go to Solution.

- Labels:

-

WICED Studio Wi-Fi Combo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

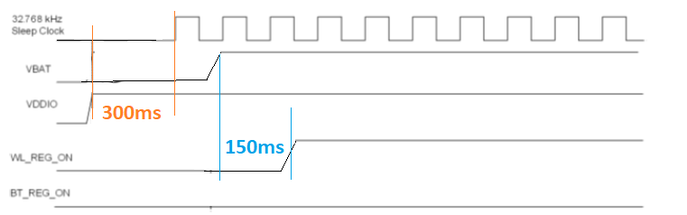

I've a difference with the module datasheet.

VDDIO is set up before the clock because VDDIO is used by the SMT32.

VBAT is not set up at the same time as VDDIO but after the clock.

Is it a problem? I've the same timing with STM32 Connectivity Pack and it's working.

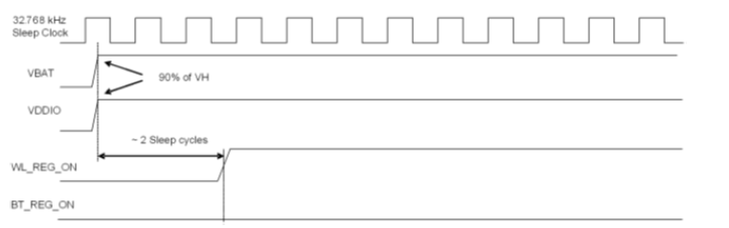

Datasheet:

My custom board:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried to get the chip log with the function "read_wlan_chip_console_log". When it works, the result is:

CONSOLE: hndarm_armr addr: 0x18003000, cr4_idx: 0

CONSOLE: 000000.002

CONSOLE: RTE (V-CDC) 7.45.98.50 (r688715 CY) on BCM43430 r1 @ 37.4/81.6/81.6MHz

CONSOLE: 000000.003 sdpcmdcdc0: Broadcom SDPCMD CDC driver

CONSOLE: 000000.004

CONSOLE: FWID 01-283fcdb9

CONSOLE: flags 1

CONSOLE: 000000.005

CONSOLE: TRAP 3(6fe9c): pc 46696, lr 3edfb, sp 6fef0, cpsr 3, spsr 1000000

CONSOLE: 000000.006 r0 b6, r1 18001000, r2 0, r3 43e2, r4 3d90c, r5 43e2, r6 4668d

CONSOLE: 000000.008 r7 3d90c, r8 25, r9 4, r10 25, r11 1, r12 8

CONSOLE: 000000.009

CONSOLE: sp+0 000000b6 18001000 00000000 000043e2

CONSOLE: 000000.010 sp+10 00000008 0003edfb 00046696 01000000

CONSOLE:

CONSOLE: 000000.011 sp+f4 000048a3

CONSOLE: 000000.011 sp+fc 0000230b

It only works when the HT clock is working. I dont have the error when it works. But I have another error

Timeout while waiting for function 2 to be ready

Could not initialize bus

Could not initialize wifi platform

WWD SDIO interface initialization FAILED: result 2Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found the problem. In STM32H7 DMA must be 32 bits aligned.