- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I've downloaded firmware reference design SlaveFifoSync, generated SF_shrt_ZLP.img.

Made below changes to FPGA example slaveFIFO2b_fpga (VHDL version) code, generated bit file.

1. Force mode to ZLP.

2. Tied flagc and flagd to gnd.

3. Add debug LED and probe signals.

I can program firmware.

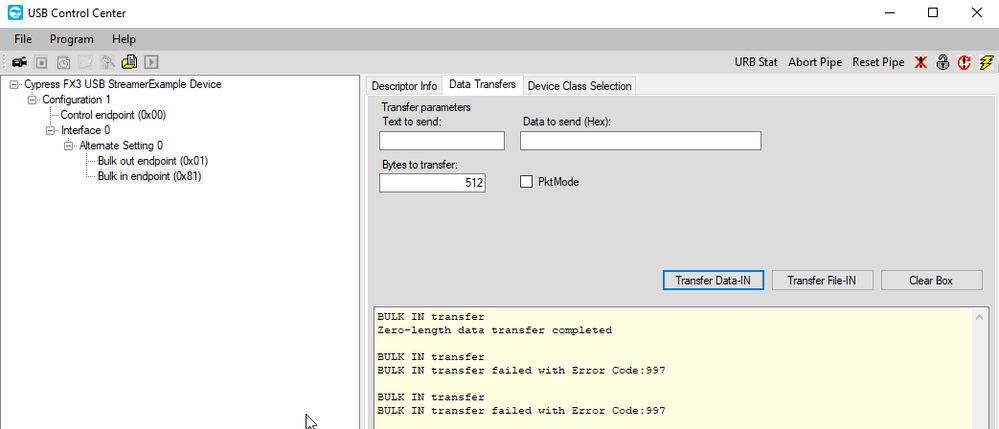

Except one complete transfer, "Transfer Data-IN" always fail.

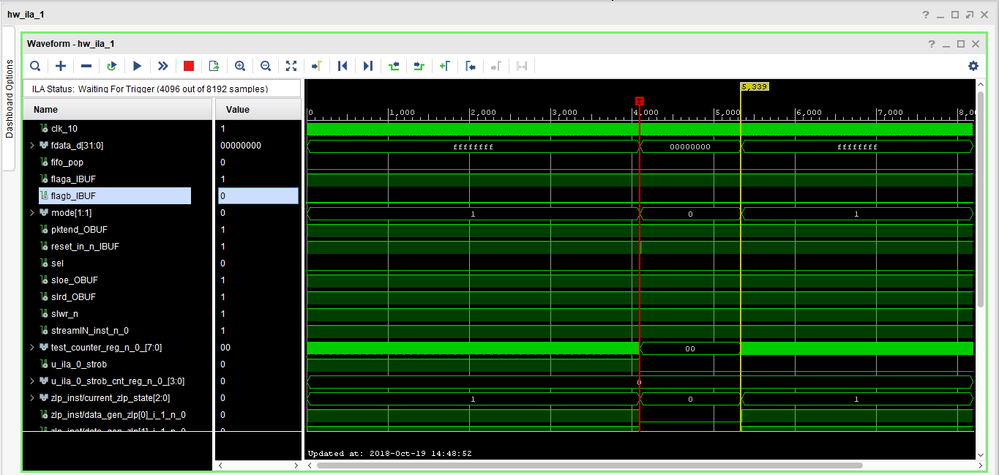

Noticed flagb is always low.

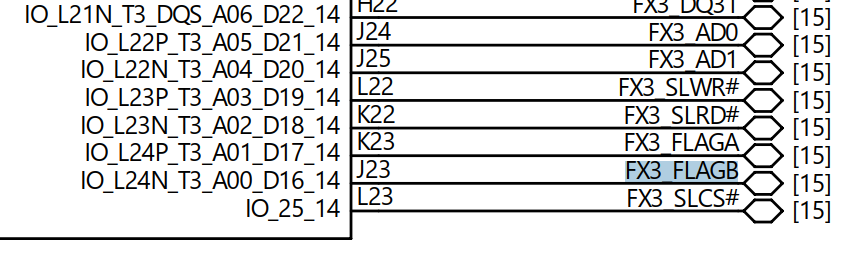

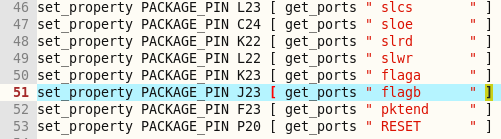

Checked pin location constraint is matching with schematic.

Why flagb is always low? How to fix this?

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If I change FPGA code, tied flaga and flagb together, FX3 can receive data from FPGA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

-Please share the simulation wave-forms,when tied flag_a and flag_b together.

- Did you make any modifications to the application note firmware An65974? If yes, please mention the same.

- Can you please check if the flagb was always zero from power on? If not, please provide the interface timing diagram before and after the flagb is going low.

- Did you make any modifications to the watermark value?

- Are you seeing any PIB underrun or overrun error when the flag status changed to low?

Regards,

Anil Srinivas.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anil,

Currently I just run FPGA test.

Below is the waves captured with trigger fdata_d != 32'hFFFF_FFFF.

Not sure how to attach exported ila file.

Data in "USB Control Center" looks okay, not sure why fdata_d doesn't start with 0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Seems after power on, FX3 will receive the first packet with data started with 0.

But when I click capture in Xilinx Vivado, it's capturing second packet.

So after power on board, I need to hard reset FPGA and click "Transfer Data-IN", after this waves data are matching with "USB Control Center" data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anil,

1. I didn't change the SlaveFifoSync firmware.

2. Not sure how to check flagb from power on. Since it's an "internal" signal. The only way I can check flagb is through Xilinx Vivado probe. I can capture flagb signal before/after board hard reset. Please let me know if you need it.

3. Not sure about "watermark value", if it's related to why first data is not 0, I think I found the answer.

4. Not sure what's "PIB underrun or overrun error", I didn't notice any error/warning message from "USB Control Center".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Dong Chen,

-The Backflow(overrun & underrun error)error comes, when the DMA buffers get filled and the GPIF is still trying to write the data. If the host is reading the data slower than the data being written at the GPIF interface, then the DMA buffers will get filled and give this Backflow(overrun & underrun error).

Regard,

Anil Srinivas.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anil,

Could you message your company email to me, it's not easy to attach file here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anil,

Thanks for the Backflow definition.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Dong Chen,

--Please provide the flagb signal timing diagram before/after board hard reset.

Regards,

Anil Srinivas.