- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are using EZ-USB FX3 as slave FIFO to connect FPGA. We know EZ USB SDK provide firmware project for this application, named SlaveFifoSync. The parameter "CY_FX_SLFIFO_GPIF_16_32BIT_CONF_SELECT" in cyfxslfifosync.h is "0", meaning 16bit GPIF data bus.

But In our design, We need 32bit GPIF data bus. When we change the parameter "CY_FX_SLFIFO_GPIF_16_32BIT_CONF_SELECT" value from "0" to "1", build project, and download .img file to board. The column on the left is blank even if project programming succeeded.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

In case you had connected the FX3 board to an external device (such as an FPGA), make sure the FPGA is not programmed before programming the FX3. This is because the FPGA may drive the PMODE lines of the FX3 and hence the enumeration of FX3 would fail.

Best regards,

Srinath S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

When the GPIF II is configured for 32 bit, the SPI interface is not available on the FX3. This can be found from the Pin Configuration section of the FX3 Datasheet. So, when configuring the GPIF II for 32-bits, the useSpi parameter in the io_cfg should be set to CyFalse. Kindly, modify this parameter, build and test it. It should work fine.

Best regards,

Srinath S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Can you please post the code snippet in the main() function?

Best regards,

Srinath S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, the code about io_cfg in main():

/* Configure the IO matrix for the device. On the FX3 DVK board, the COM port

is connected to the IO(53:56). This means that either DQ32 mode should be

selected or lppMode should be set to UART_ONLY. Here we are choosing

UART_ONLY configuration for 16 bit slave FIFO configuration and setting

isDQ32Bit for 32-bit slave FIFO configuration. */

io_cfg.s0Mode = CY_U3P_SPORT_INACTIVE;

io_cfg.s1Mode = CY_U3P_SPORT_INACTIVE;

io_cfg.useUart = CyTrue; /////CyTrue

io_cfg.useI2C = CyFalse;

io_cfg.useI2S = CyFalse;

io_cfg.useSpi = CyFalse;

#if (CY_FX_SLFIFO_GPIF_16_32BIT_CONF_SELECT == 0)

io_cfg.isDQ32Bit = CyFalse;

io_cfg.lppMode = CY_U3P_IO_MATRIX_LPP_UART_ONLY;

#else

io_cfg.isDQ32Bit = CyTrue;

io_cfg.lppMode = CY_U3P_IO_MATRIX_LPP_DEFAULT;

#endif

/* No GPIOs are enabled. */

io_cfg.gpioSimpleEn[0] = 0;

io_cfg.gpioSimpleEn[1] = 0;

io_cfg.gpioComplexEn[0] = 0;

io_cfg.gpioComplexEn[1] = 0;

status = CyU3PDeviceConfigureIOMatrix (&io_cfg); /////////

if (status != CY_U3P_SUCCESS)

{

goto handle_fatal_error;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

In the handle_fatal_error code section, can you add the below API call and check if the device is reset and falls back to boot-loader. This would help us identify if the issue is with the device initialization.

CyU3PDeviceReset(CyFalse);

Best regards,

Srinath S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

LIKE this "

if (status != CY_U3P_SUCCESS)

{

CyU3PDeviceReset(CyFalse);

goto handle_fatal_error;

} "??

There is a problem. I only can build this project, can't debug it. So I can't get the process information judge whether the device is reset .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please modify the below part of the code

handle_fatal_error:

/* Cannot recover from this error. */

while (1);

to

handle_fatal_error:

/* Cannot recover from this error. */

CyU3PDeviceReset(CyFalse);

while (1);

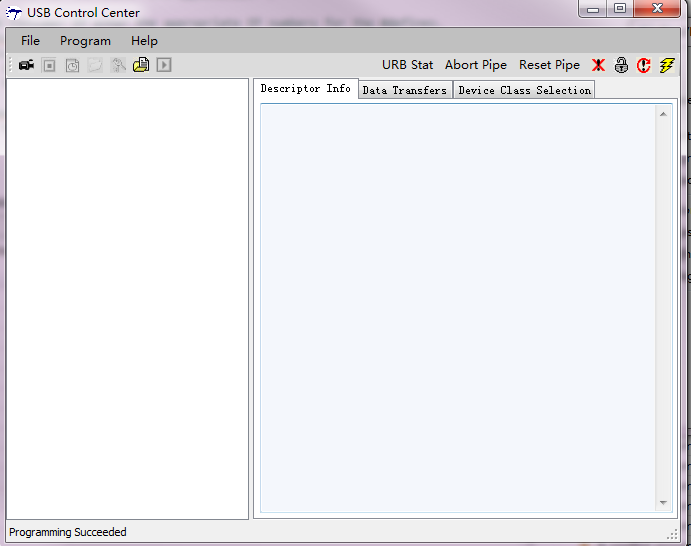

After this modification, build the project and load the firmware into the device using the Cypress USB Control Center. If the Control Center shows the device as Cypress FX3 Bootloader Device it means that the device is reset by the added statement. This can help us identify if there is an error in the initialization part.

Also, I assume that you have not modified the slaveFifoSync example that comes with the FX3 SDK. In case you have made any changes, please let me know.

Best regards,

Srinath S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Updating firmare according to your mentioned before,

The code run result is that ?

status = CyU3PDeviceConfigureIOMatrix (&io_cfg);

the status is fail because some parameter of io_cfg configuration fail? but "io_cfg.isDQ32Bit" configured successfully? Is it TURE?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

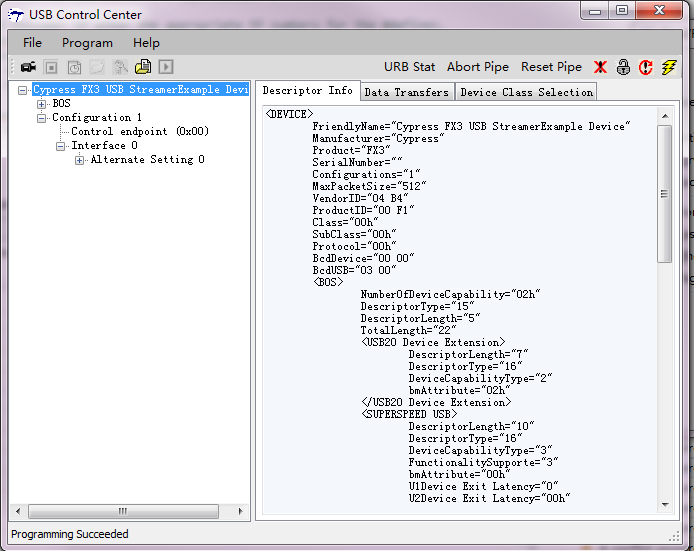

I add the statement like you said. Build, download to FX3 RAM, and then, the result appear in control center, as shown below.

I don't make any modification on slaveFifoSync example that comes with the FX3 SDK, except that " CY_FX_SLFIFO_GPIF_16_32BIT_CONF_SELECT" in cyfxslfifosync.h from 0 to 1.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Use the main function in the firmware as below and check if the device comes up in the Control Center.

int

main (void)

{

CyU3PIoMatrixConfig_t io_cfg;

CyU3PReturnStatus_t status = CY_U3P_SUCCESS;

CyU3PSysClockConfig_t clockConfig;

/* When the GPIF data bus is configured as 32-bits wide and running at 100 MHz (synchronous),

the FX3 system clock has to be set to a frequency greater than 400 MHz. */

#if (CY_FX_SLFIFO_GPIF_16_32BIT_CONF_SELECT == 0)

clockConfig.setSysClk400 = CyFalse;

#else

clockConfig.setSysClk400 = CyTrue;

#endif

clockConfig.cpuClkDiv = 2;

clockConfig.dmaClkDiv = 2;

clockConfig.mmioClkDiv = 2;

clockConfig.useStandbyClk = CyFalse;

clockConfig.clkSrc = CY_U3P_SYS_CLK;

status = CyU3PDeviceInit (&clockConfig);

if (status != CY_U3P_SUCCESS)

{

goto handle_fatal_error;

}

/* Initialize the caches. Enable both Instruction and Data Caches. */

status = CyU3PDeviceCacheControl (CyTrue, CyTrue, CyTrue);

if (status != CY_U3P_SUCCESS)

{

goto handle_fatal_error;

}

/* Configure the IO matrix for the device. On the FX3 DVK board, the COM port

* is connected to the IO(53:56). This means that either DQ32 mode should be

* selected or lppMode should be set to UART_ONLY. Here we are choosing

* UART_ONLY configuration for 16 bit slave FIFO configuration and setting

* isDQ32Bit for 32-bit slave FIFO configuration. */

io_cfg.s0Mode = CY_U3P_SPORT_INACTIVE;

io_cfg.s1Mode = CY_U3P_SPORT_INACTIVE;

io_cfg.useUart = CyTrue;

io_cfg.useI2C = CyFalse;

io_cfg.useI2S = CyFalse;

io_cfg.useSpi = CyFalse;

#if (CY_FX_SLFIFO_GPIF_16_32BIT_CONF_SELECT == 0)

io_cfg.isDQ32Bit = CyFalse;

io_cfg.lppMode = CY_U3P_IO_MATRIX_LPP_UART_ONLY;

#else

io_cfg.isDQ32Bit = CyTrue;

io_cfg.lppMode = CY_U3P_IO_MATRIX_LPP_DEFAULT;

#endif

/* No GPIOs are enabled. */

io_cfg.gpioSimpleEn[0] = 0;

io_cfg.gpioSimpleEn[1] = 0;

io_cfg.gpioComplexEn[0] = 0;

io_cfg.gpioComplexEn[1] = 0;

status = CyU3PDeviceConfigureIOMatrix (&io_cfg);

if (status != CY_U3P_SUCCESS)

{

goto handle_fatal_error;

}

/* This is a non returnable call for initializing the RTOS kernel */

CyU3PKernelEntry ();

/* Dummy return to make the compiler happy */

return 0;

handle_fatal_error:

/* Cannot recover from this error. */

while (1);

}

Best regards,

Srinath S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

In case you had connected the FX3 board to an external device (such as an FPGA), make sure the FPGA is not programmed before programming the FX3. This is because the FPGA may drive the PMODE lines of the FX3 and hence the enumeration of FX3 would fail.

Best regards,

Srinath S