- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The datasheet of FX3 says for synchronous slave FIFO read, the data becomes valid in tco after the rising edge PCLK (from FPGA to FX3). I find the data becomes valid in tco after the falling edge PCLK, I draw this conclusion from 2 sources. 1) The captured FPGA internal signal

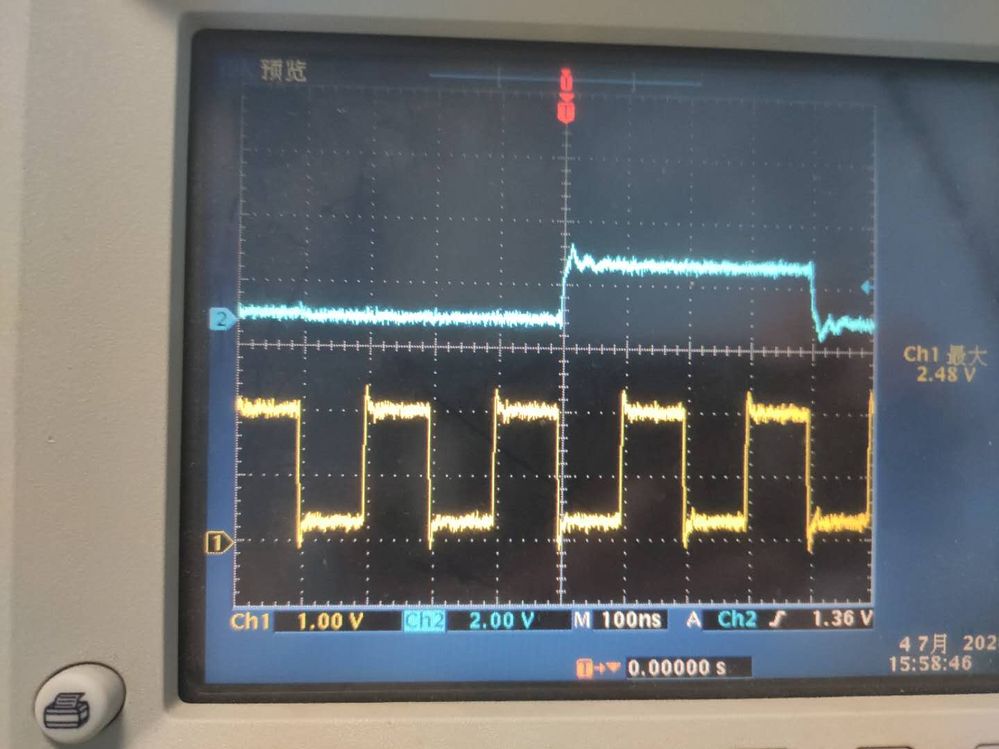

2) The PCLK and data signal captured at the PCB, from FPGA to FX3, as follows. The blue signal is the least significant data bit.

I guess FX3 devices may be updated and the document may not be updated, leading to the difference between description and actual behavior of the devices. Is my understanding correct?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

This seems to be causing the issue that you are seeing on your end.

The default slaveFifo Sync state machine comes with a Positive Active Clock edge.

Also, you would need to make sure the FPGA follows the positive clock edge and all other parameters accordingly.

Please change this and build the project to get the cyfxgpif2config.h file.

Replace the old gpif2config.h file in your workspace with the newly generated config.h file and clean build the project again.

Please try with the latest image with Active Clock Edge: Positive and see if you get the expected results.

PS: For your reference, I have added the modified cyfxgpif2config.h file with Positive Active Clock edge. You can replace the old file with the one attached to this interaction.

Regards,

Yashwant