- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to connect a Cypress Fx3 superspeed kit with a FPGA board using the synchronous slave FIFO 2bit example.

Data TX(FPGA → FX3) using slave FIFO.

However, after started to TX data from the FPGA, Flag A is high and it does not change its value. (FIFO ADDRESS Value 0b00)

And PKTEND# is working but PtoU Call Back function is not working.

I already checked the constraints and board PINs according to the documentation are well.

Do you know any idea in this problem?

epCfg.enable = CyTrue;

epCfg.epType = CY_U3P_USB_EP_BULK;

epCfg.burstLen = 1;

epCfg.streams = 0;

epCfg.pcktSize = 1024;

CyU3PSetEpConfig(CY_FX_EP_PRODUCER, &epCfg);

CyU3PSetEpConfig(CY_FX_EP_CONSUMER, &epCfg);

dmaCfg.size = 1024;

dmaCfg.count = 2;

dmaCfg.prodSckId = CY_FX_PRODUCER_USB_SOCKET;

dmaCfg.consSckId = CY_FX_CONSUMER_PPORT_SOCKET;

dmaCfg.dmaMode = CY_U3P_DMA_MODE_BYTE;

dmaCfg.notification = CY_U3P_DMA_CB_PROD_EVENT;

dmaCfg.cb = CyFxSlFifoUtoPDmaCallback;

dmaCfg.prodHeader = 0;

dmaCfg.prodFooter = 0;

dmaCfg.consHeader = 0;

dmaCfg.prodAvailCount = 0;

CyU3PDmaChannelCreate (&glChHandleSlFifoUtoP,CY_U3P_DMA_TYPE_MANUAL, &dmaCfg);

dmaCfg.prodSckId = CY_FX_PRODUCER_PPORT_SOCKET;

dmaCfg.consSckId = CY_FX_CONSUMER_USB_SOCKET;

dmaCfg.cb = CyFxSlFifoPtoUDmaCallback;

CyU3PDmaChannelCreate (&glChHandleSlFifoPtoU,CY_U3P_DMA_TYPE_MANUAL, &dmaCfg);

#define CY_FX_EP_PRODUCER 0x01 /* EP 1 OUT */

#define CY_FX_EP_CONSUMER 0x81 /* EP 1 IN */

#define CY_FX_PRODUCER_USB_SOCKET CY_U3P_UIB_SOCKET_PROD_1 /* USB Socket 1 is producer */

#define CY_FX_CONSUMER_USB_SOCKET CY_U3P_UIB_SOCKET_CONS_1 /* USB Socket 1 is consumer */

#define CY_FX_PRODUCER_PPORT_SOCKET CY_U3P_PIB_SOCKET_0 /* P-port Socket 0 is producer */

#define CY_FX_CONSUMER_PPORT_SOCKET CY_U3P_PIB_SOCKET_3 /* P-port Socket 3 is consumer */

GPIF 32bit mode and PCLK 100Mhz

clockConfig.cpuClkDiv = 2;

clockConfig.dmaClkDiv = 2;

clockConfig.mmioClkDiv = 2;

clockConfig.useStandbyClk = CyFalse;

clockConfig.clksrc=CY_U3P_SYS_CLK;

status = CyU3PDeviceInit (&clockConfig);

- Labels:

-

USB Superspeed Peripherals

- Tags:

- FLAGA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please have a look at the given thread : https://community.cypress.com/t5/Knowledge-Base-Articles/Debugging-when-DMA-Flags-do-not-Work-as-Exp... as well as the Troubleshooting section in the updated AN65974.

Best Regards,

AliAsgar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Okay, i will check it.

And then,

PKTEND# is working but PtoU Call Back function is not working.

What should i check?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you drive a GPIO in the state where commit is taking place after PKTEND is asserted and let us know if the GPIO is driven during the operation. This will give us an idea whether the PKTEND is getting read by FX3 properly.

Best Regards,

AliAsgar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

CyFxSlFifoPtoUDmaCallback function is not called after PKTEND.

So, even if i change the GPIO state where commit function, i can't check it.

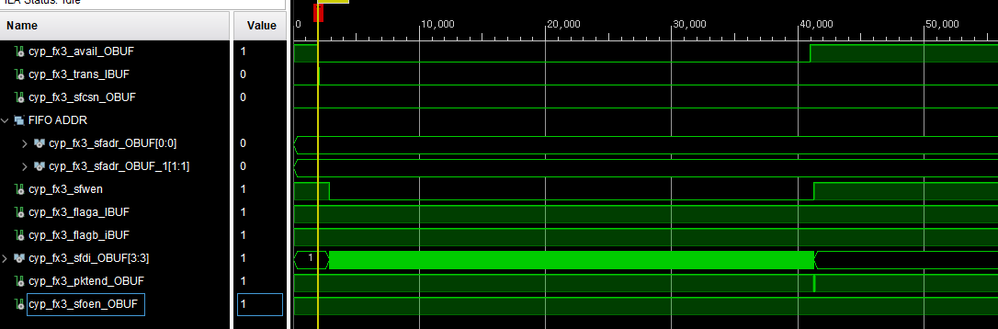

PKTEND, SLCS#, SLWR#, SLOE# signal is normally checked below.

※FX3 input FIFO address

CTL12(Address0) = 0, CTL11(Address1) = 0

※PtoU call back function

/* DMA callback function to handle the produce events for P to U transfers. */

void CyFxSlFifoPtoUDmaCallback ( CyU3PDmaChannel *chHandle, CyU3PDmaCbType_t type, CyU3PDmaCBInput_t *input)

{

CyU3PReturnStatus_t status = CY_U3P_SUCCESS;

CyU3PDebugPrint (4, "CyFxSlFifoPtoUDmaCallback start\r\n");

// It dosen't call after PKTEND

if (type == CY_U3P_DMA_CB_PROD_EVENT)

{

status = CyU3PDmaChannelCommitBuffer (chHandle, input->buffer_p.count, 0);

}

}

※DMA setting

dmaCfg.size = 16384;

dmaCfg.count = CY_FX_SLFIFO_DMA_BUF_COUNT;

dmaCfg.dmaMode = CY_U3P_DMA_MODE_BYTE;

dmaCfg.notification = CY_U3P_DMA_CB_PROD_EVENT;

dmaCfg.prodHeader = 0;

dmaCfg.prodFooter = 0;

dmaCfg.consHeader = 0;

dmaCfg.prodAvailCount = 0;

/* Create a DMA MANUAL channel for P2U transfer. */

dmaCfg.prodSckId = CY_U3P_PIB_SOCKET_0;

dmaCfg.consSckId = CY_U3P_UIB_SOCKET_CONS_1;

dmaCfg.cb = CyFxSlFifoPtoUDmaCallback;

apiRetStatus = CyU3PDmaChannelCreate (&glChHandleSlFifoPtoU, CY_U3P_DMA_TYPE_MANUAL, &dmaCfg);

※GPIF code

/*

* Project Name: GPIFII_Designer_sync_SlaveFIFO.cyfx

* Time : 12/01/2016 14:22:45

* Device Type: FX3

* Project Type: GPIF2

*

*

*

*

* This is a generated file and should not be modified

* This file need to be included only once in the firmware

* This file is generated by Gpif2 designer tool version - 1.0.1198.2

*

*/

#ifndef _INCLUDED_GPIFII_DESIGNER_SYNC_SLAVEFIFO_CYDSN_

#define _INCLUDED_GPIFII_DESIGNER_SYNC_SLAVEFIFO_CYDSN_

#include "cyu3types.h"

#include "cyu3gpif.h"

/* Summary

Number of states in the state machine

*/

#define CY_NUMBER_OF_STATES 7

/* Summary

Mapping of user defined state names to state indices

*/

#define RESET 0

#define IDLE 1

#define READ 2

#define WRITE 3

#define SHORT_PKT 4

#define ZLP 5

#define DSS_STATE 6

/* Summary

Initial value of early outputs from the state machine.

*/

#define ALPHA_RESET 0xC

/* Summary

Transition function values used in the state machine.

*/

uint16_t CyFxGpifTransition[] = {

0x0000, 0x8080, 0x2222, 0x5555, 0x7F7F, 0x1F1F, 0x8888

};

/* Summary

Table containing the transition information for various states.

This table has to be stored in the WAVEFORM Registers.

This array consists of non-replicated waveform descriptors and acts as a

waveform table.

*/

CyU3PGpifWaveData CyFxGpifWavedata[] = {

{{0x1E086001,0x000302C4,0x80000000},{0x00000000,0x00000000,0x00000000}},

{{0x4E080302,0x00000300,0x80000000},{0x1E086006,0x000302C4,0x80000000}},

{{0x1E086001,0x000302C4,0x80000000},{0x4E040704,0x20000300,0xC0100000}},

{{0x4E080302,0x00000300,0x80000000},{0x1E086001,0x000302C4,0x80000000}},

{{0x00000000,0x00000000,0x00000000},{0x00000000,0x00000000,0x00000000}},

{{0x00000000,0x00000000,0x00000000},{0x3E738705,0x00000300,0xC0100000}},

{{0x00000000,0x00000000,0x00000000},{0x5E002703,0x2003030C,0x80000000}},

{{0x00000000,0x00000000,0x00000000},{0x4E040704,0x20000300,0xC0100000}}

};

/* Summary

Table that maps state indices to the descriptor table indices.

*/

uint8_t CyFxGpifWavedataPosition[] = {

0,1,0,2,0,0,3,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,

4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,

0,5,0,2,0,0,5,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,

4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,

0,6,0,2,0,0,6,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,

4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,4,

0,7,0,2,0,0,7

};

/* Summary

GPIF II configuration register values.

*/

uint32_t CyFxGpifRegValue[] = {

0x80000380, /* CY_U3P_PIB_GPIF_CONFIG */

0x000010AC, /* CY_U3P_PIB_GPIF_BUS_CONFIG */

0x01070002, /* CY_U3P_PIB_GPIF_BUS_CONFIG2 */

0x00000044, /* CY_U3P_PIB_GPIF_AD_CONFIG */

0x00000000, /* CY_U3P_PIB_GPIF_STATUS */

0x00000000, /* CY_U3P_PIB_GPIF_INTR */

0x00000000, /* CY_U3P_PIB_GPIF_INTR_MASK */

0x00000082, /* CY_U3P_PIB_GPIF_SERIAL_IN_CONFIG */

0x00000782, /* CY_U3P_PIB_GPIF_SERIAL_OUT_CONFIG */

0x00011500, /* CY_U3P_PIB_GPIF_CTRL_BUS_DIRECTION */

0x0000FE8F, /* CY_U3P_PIB_GPIF_CTRL_BUS_DEFAULT */

0x000001FF, /* CY_U3P_PIB_GPIF_CTRL_BUS_POLARITY */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_TOGGLE */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000010, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000014, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000013, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000017, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_BUS_SELECT */

0x00000006, /* CY_U3P_PIB_GPIF_CTRL_COUNT_CONFIG */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_COUNT_RESET */

0x0000FFFF, /* CY_U3P_PIB_GPIF_CTRL_COUNT_LIMIT */

0x0000010A, /* CY_U3P_PIB_GPIF_ADDR_COUNT_CONFIG */

0x00000000, /* CY_U3P_PIB_GPIF_ADDR_COUNT_RESET */

0x0000FFFF, /* CY_U3P_PIB_GPIF_ADDR_COUNT_LIMIT */

0x00000000, /* CY_U3P_PIB_GPIF_STATE_COUNT_CONFIG */

0x0000FFFF, /* CY_U3P_PIB_GPIF_STATE_COUNT_LIMIT */

0x0000010A, /* CY_U3P_PIB_GPIF_DATA_COUNT_CONFIG */

0x00000000, /* CY_U3P_PIB_GPIF_DATA_COUNT_RESET */

0x0000FFFF, /* CY_U3P_PIB_GPIF_DATA_COUNT_LIMIT */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_COMP_VALUE */

0x00000000, /* CY_U3P_PIB_GPIF_CTRL_COMP_MASK */

0x00000000, /* CY_U3P_PIB_GPIF_DATA_COMP_VALUE */

0x00000000, /* CY_U3P_PIB_GPIF_DATA_COMP_MASK */

0x00000000, /* CY_U3P_PIB_GPIF_ADDR_COMP_VALUE */

0x00000000, /* CY_U3P_PIB_GPIF_ADDR_COMP_MASK */

0x00000000, /* CY_U3P_PIB_GPIF_DATA_CTRL */

0x00000000, /* CY_U3P_PIB_GPIF_INGRESS_DATA */

0x00000000, /* CY_U3P_PIB_GPIF_INGRESS_DATA */

0x00000000, /* CY_U3P_PIB_GPIF_INGRESS_DATA */

0x00000000, /* CY_U3P_PIB_GPIF_INGRESS_DATA */

0x00000000, /* CY_U3P_PIB_GPIF_EGRESS_DATA */

0x00000000, /* CY_U3P_PIB_GPIF_EGRESS_DATA */

0x00000000, /* CY_U3P_PIB_GPIF_EGRESS_DATA */

0x00000000, /* CY_U3P_PIB_GPIF_EGRESS_DATA */

0x00000000, /* CY_U3P_PIB_GPIF_INGRESS_ADDRESS */

0x00000000, /* CY_U3P_PIB_GPIF_INGRESS_ADDRESS */

0x00000000, /* CY_U3P_PIB_GPIF_INGRESS_ADDRESS */

0x00000000, /* CY_U3P_PIB_GPIF_INGRESS_ADDRESS */

0x00000000, /* CY_U3P_PIB_GPIF_EGRESS_ADDRESS */

0x00000000, /* CY_U3P_PIB_GPIF_EGRESS_ADDRESS */

0x00000000, /* CY_U3P_PIB_GPIF_EGRESS_ADDRESS */

0x00000000, /* CY_U3P_PIB_GPIF_EGRESS_ADDRESS */

0x80010400, /* CY_U3P_PIB_GPIF_THREAD_CONFIG */

0x80010401, /* CY_U3P_PIB_GPIF_THREAD_CONFIG */

0x80010402, /* CY_U3P_PIB_GPIF_THREAD_CONFIG */

0x80010403, /* CY_U3P_PIB_GPIF_THREAD_CONFIG */

0x00000000, /* CY_U3P_PIB_GPIF_LAMBDA_STAT */

0x00000000, /* CY_U3P_PIB_GPIF_ALPHA_STAT */

0x00000000, /* CY_U3P_PIB_GPIF_BETA_STAT */

0x000C0000, /* CY_U3P_PIB_GPIF_WAVEFORM_CTRL_STAT */

0x00000000, /* CY_U3P_PIB_GPIF_WAVEFORM_SWITCH */

0x00000000, /* CY_U3P_PIB_GPIF_WAVEFORM_SWITCH_TIMEOUT */

0x00000000, /* CY_U3P_PIB_GPIF_CRC_CONFIG */

0x00000000, /* CY_U3P_PIB_GPIF_CRC_DATA */

0xFFFFFFC1 /* CY_U3P_PIB_GPIF_BETA_DEASSERT */

};

/* Summary

This structure holds all the configuration inputs for the GPIF II.

*/

const CyU3PGpifConfig_t CyFxGpifConfig = {

(uint16_t)(sizeof(CyFxGpifWavedataPosition)/sizeof(uint8_t)),

CyFxGpifWavedata,

CyFxGpifWavedataPosition,

(uint16_t)(sizeof(CyFxGpifTransition)/sizeof(uint16_t)),

CyFxGpifTransition,

(uint16_t)(sizeof(CyFxGpifRegValue)/sizeof(uint32_t)),

CyFxGpifRegValue

};

#endif /* _INCLUDED_GPIFII_DESIGNER_SYNC_SLAVEFIFO_CYDSN_ */

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

What I meant is, in the GPIF II State Machine, to whichever state there is a transition, after PKTEND is asserted. Perform a DR_GPIO action in that state. This will tell us whether the states are getting transitioned properly based on the PKTEND signal.

Best Regards,

AliAsgar