USB EZ-PD™ Type-C Forum Discussions

I am testing PPS using QuadMax,

it shows two faied items :

1. PUT did not maintain voltage under tester

2. Current did not settle to iPpsCLNew within tPpsCLSettle

What does it mean and how to fix this problem ?

Show LessHi.Cypress

客户有拿到市场的apple 30W adapter(另外60W苹果也有类似情况,正在让客户测试和收集详细信息)给到参考PB812B设计的方案进行充电,使用抓包仪器,发现无任何协议沟通,无法充电,使用他们分别跟其他设备充电或者放电都是正常的。抓取到的CC波形如附件。请帮忙告之在PB812B的代码要增加或者修改哪些语句呢?

thanks

flance fang

Show LessHi,

So after 7 months of asking for support we still have no information on how to roll our own firmware for this PD hub controller, everytime we ask for help we get an email asking how many millions of units will we be buying anytime soon.

Yes this is a JOKE to some sales guys that work at cypress, we need to make a working proto before we even know if customers will accept this solution ...

possibly someone would be nice enough to let us know how to deal with boards we built based on hundreds of emails between cypress and our tech design team . our design is not standard reference it uses MPQ4230 buck/boost IC so therefore we need to be able to build our own firmware , we have other MPQ 3171 working firmware so we feel comfortable porting it over if we had some help

Please HELP

-------------------------- where we are now

Board is built and working (for the most part)

Design is currently accepting firmware as described in

EZ-USB® HX3PD Configuration Utility

Release Notes

Version 1.0 Alpha, March 28, 2018

we have hub identified in device mgr.

we can pass usb HS data to all ports (mux not working due to polarity report in PD section we assume)

no PD power due to MPQ power Section instead of reference OnSemi, we also have a total of three PD ports so we used a standard CYPD3171 for our UFP port power

------------ what we need

just some help in building the MPQ firmware for this specific IC CYUSB4347-BZXC

Show LessHello,

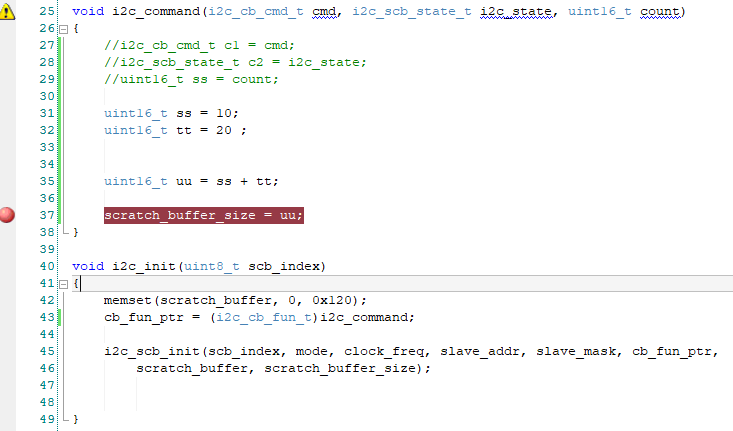

I want to use my pc to connect cypd3125. However the HPI Interface not open,and then I deleted the hpi code and try to use I2c connect directly. But I got nothing.

In my PC,I use “CyI2cWrite” to send data。

And cypd3125 in cy4531, I use callback in "i2c_scb_init" to get data.

And I set breakpoint in i2c_command, then use cyi2cwrite to send data, but not stoped. (I call i2c_init in main function).

thanks.

Show LessHello,

We use CY4501 REV 07 development board before, but we purchased CY4501 REV 08 this year, this version REV 08 can't match soft Garter_Tester_v1.0.4, please tell me how to solve, or provide new test soft.

Dear,

I made a dock and used the CYPD4236-40LQXI_dock sample code.

Stopped in step 8 when entering DisplayPort Alternate Mode.

I can't see the "DP_Status_update" sent from my laptop.

How to solve this error?

This is PASS case.

This is fail case.

https://community.cypress.com/message/204704#204704

MaLi_3529141 2019/8/2 上午 2:35

Dear,

I made a dock and used the CYPD4236-40LQXI_dock sample code.

Stopped in step 9 when entering DisplayPort Alternate Mode

I’m working with the CYPD3175-24LQXQ_pa_direct_fb project for the CCG3PA, on custom HW. I have a separate supply for the CCG3PA VDDD (3.3V) and the VBUS source regulator. The firmware is somewhat functional on my HW but I see strange behavior. After the controller enables the VBUS source by asserting a GPIO to the regulator’s pin (and VBUS goes to 5V), when I then disable the VBUS source I see 3.3V remaining on the VBUS line. The 3.3V is coming from the CCG3PA somewhere (verified by shutting down the power to the VBUS source regulator).

Any ideas what could cause the 3.3V to show up on the VBUS line? The CCG3PA has pins VBUS_C_MON_DISCHARGE and VBUS_IN_DISCHARGE connected to the VBUS line, per the reference schematic in the CCG3PA datasheet. My guess is that it has something to do with the ability of the CCG3PA to derive VDDD from VBUS_IN_DISCHARGE, that somehow the 3.3V on VDDD is getting fed back to this pin?

Show LessOur customer have INTEL account to download INTEL reference design document.

But we just find TI + TitanRidge host schematic.

Base on below Cypress web information, Intel should have Cypress solution available.

Could you share INTEL document number or something key word to help us find it for download?

Thanks,

Mitchell

Show LessHi, I would like clarification on the use of the VDC_OUT pin on CYPD3177. I will be using this in a system where the main VBUS gate is not controlled by CYPD3177. So, VBUS_FET_EN and SAFE_POWER_EN will remain disconnected.

I would like to know the expected operation of CYPD3177 if VDC_OUT is left floating, grounded, tied to VBUS_IN, etc.

I would also like assurance that the D+/D- pins can be placed in parallel with a typical USB2 HS device, as this is not specified in the datasheet and the development board does not break out these pins.

Thank you

Show Less