USB EZ-PD™ Type-C Forum Discussions

我们正在设计一种通过使用 CYPD4226 PD 控制器来控制 TUSB1064 的方法,以便它可以在 DP alt 模式下运行。我们通过 I2C 模式配置了 TUSB1064 的寄存器0x0A和0x13,并将其配置为四 DP 通道无 Filp,如下所示。此外,VUBS也是没有电源的配置,但是通过使用CY4500分析仪,我们得到的结果是这样的。我不知道问题是什么,请指教。所有工程文件都已打包,请告知。

Hi,

I am looking use PD-EPR for 140W support in a sink application. Is there any plan to update the CYPD3177 to support EPR?

Thanks in advance.

Show LessHi

I have looked at the Kit Guide for the CY4521 and I have the following questions.

1.Does CY7C65215 have a specific firmware so that it can communicate with CYPD2122 and be programmed in EZPD?

2.Can I customize the kit according to the hardware datasheet in the manual? Is this method feasible?

3.If possible, we hope to provide the appropriate software and driver versions required for this project.

Thank

Show LessWhich USB PD Controllers, CCG or PMG, contain the logic to support Attach Detection Protocol (ADP) to detect a connected device then accept power from (sink) or provide power to (source) the connected OTG device without the benefit of a cc signal?

Stated differently; USB OTG Devices that interface through a four wire USB micro or USB A connector, may be connected via a physical adapter to a USB-C interface controlled by an Infineon USB PD Controller. Can Infineon's USB PD Controller support OTG devices?

"ADP operates by detecting the change in VBUS capacitance that occurs when two devices are attached or detached. The capacitance is detected by first discharging the VBUS line, and then measuring the time it takes VBUS to charge to a known voltage with a known current source. A change in capacitance is detected by looking for a change in the charge time."

Reference Section 5.4.1 of the USB "On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification" Revision 2.0 version 1.1a July 27, 2012

Greg

Show Less

Hello all,

I have a requirement to change the i2c configuration of ccg3pa in runtime ie., from I2C Multi-Master configuration to I2C slave.

From PSOC4 Serial Communication Block(SCB) document,

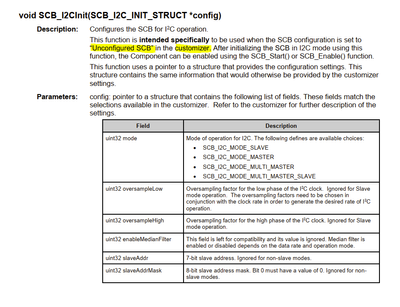

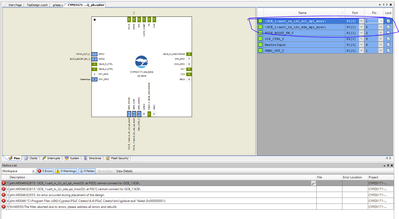

void SCB_I2CInit(SCB_I2C_INIT_STRUCT *config) description as in Image 1 says that this function is intended specifically for "Unconfigured SCB " in customizer as in Image 2,

So if I use "I2C" block instead of "Unconfigured SCB", how would I re-configure I2C from multi-master to slave mode in runtime ? Is it possible ?

And Even though if I use "Unconfigured SCB " in customizer, I'm unable to Configure I2C SCL and SDA lines to my required pins in .cydwr file as in Image 3. I want to configure SCL SDA lines to 12 and pins but only 2,5,7,8 pins are only available to configure. Why ? Any dependecny with pin muxing ? How to overcome ?

Image 1:

Image 2:

Image 3:

Thanks in advance,

Regards,

Pranay

Show Less

Hi,

Our CCG3PA (CYPD3171) is setup as a power source. After negotiating a PD contract with a sink device, I can see that CCG3PA checks the VBUS voltage (input side) to make sure it is correct before turning on the external FETs for the voltage to pass the voltage to VBUS_C (output side). This is a great safety mechanism in case something wrong happens at the input side.

My question is:

What is the tolerance of the voltage check and how can it be adjusted?

In other words, if the sink device negotiated a PDO/PPS contract, what is the variance of the input voltage allowed before CCG3PA passes it over to VBUS_C (output side)?

Thanks,

Jonathan

Is there any code of CYPD4226notebook bootloadable in the two pictures? What are the differences? What's the difference between noboot, i2cboot,dummyboot, and backupfw? If I want to make a routine change, which one should I use?

Show Less

Hi, Sir,

The Customer uses CYPD5225 to implement Alder Lake platform and it doesn't have EC to interface CCG5

They plug-in type-c pen drive during system - S4 , then BB_RETIMER repsoned a I2C - NACK to CCG5.

This "NACK' causes a problem - After resume to S0, the system can't recognize this type-c pen drive.

They also test TI - PD solution, the TI - PD will retry i2c write to BB_RETEMR if BB_RETIMER repsoned a NACK.

After re-writing i2c, the BB_RETIMER will repsoned a ACK.

1. Do you have any suggestion about this problem?

2. Does FW have i2c - retry feature? how to enable it?

BR

Ivan

Show LessCurrently, cypd2122 is configured using JLINK. Programming I2C using JLINK generates a programming error (fail@Address 0x000000130 (block verification error). etc

May I ask

1.Does the cypd2122 support jink programming?

2.What is the solution to this mistake?

thank

Show LessHi,

I want ask if these three chips support Apple's fast charge protocol.

And when two USB ports are shared, the current of one USB port exceeds 100mA, and the fast charge of the other port is exits.

CCG3PA CCG3PA-NFET IP2726