USB EZ-PD™ Type-C Forum Discussions

Hello

P3.3 of CCG6SF is used as GPIO.With a resistance of 100kΩ, pull up or pull down to create a mechanism that can detect Hi/Low.

In addition, VDDIO is 3.3V.

Q1)

However, since the customer wants to reduce the number of parts, I would like to connect it directly to GND without using the 100 kΩ resistor Lo side. Is it possible?

Q2)

If possible, what is the effect on power consumption when Pull down is connected to P3.3 with 100kΩ and when it is directly connected to GND?

Best Regards

Arai

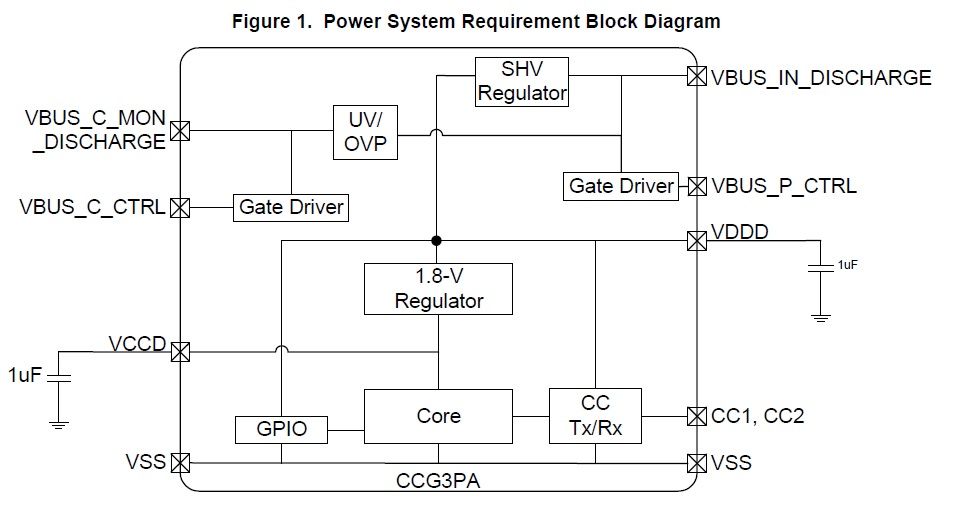

Show Less外部からVDDDを供給した場合、VBUS_IN_DISCHARGEは外部で切断してもよいでしょうか。

SHV RegulatorをOFFにしさえすればよいのでしょうか。

その時、VBUS_C_CTRLの電源供給源は何になりますでしょうか。

外部電源入力源に関係なくVBUS_C_MON_DISCAHRGEなのでしょうか。

=================================================================================

Is it possible to disconnect VBUS_IN_DISCHARGE externally when VDDD is supplied from the outside?

Is it all right if it only disable the SHV Regulator?

At that time, where is the power supply for VBUS_C_CTRL taken from?

Does VBUS_C_MON_DISCHARGE need to be supplied?

Hello,

I've been working on a USB-C monitor project utilizing a CYPD3120 to handle the USB-C DP and Power Delivery interface. We are running into some issues getting the device to actually behave as a monitor. We are able to see the device in windows as a "Generic Non-PnP Monitor", but it cannot be enabled in Display Settings, so I'm thinking something might be fishy with how the DP lanes are wired.

Our test rig consists of a CCG4 Eval Kit (CY4541) connected in DisplayPort Demo mode as described in Section 6.3 of the CCG4 EVK Guide. We have tested this with a standard retail USB-C monitor and it works without issue. This eval kit is connected by USB-C to our test board, which uses a CYPD3120 for the USB-C and a separate Bridge IC (NXP PTN3460I) to convert the (2 DP Lanes + AUX) Displayport to LVDS for output to our display panel as well as provide EDID information to the host PC via the DP AUX lines.

Our board is acting as a USB-C Monitor, not a dongle, so we are using a USB-C receptacle rather than a USB-C Plug. I suspect that maybe we have an issue with the pinout of the receptacle in regard to the DP lanes. We are intending to run the Alt-Mode DP in Mode E. Here is the schematic of our monitor input connector:

We know that the CC lines are OK, as the power delivery is working great and we are providing 15V/2.5A to the monitor board with no problems. One issue we noticed is that SBU1 is assigned to AUX- and SBU2 is assigned to AUX+, which is the reverse of what it should be. Luckily we were able to account for this in the CYPD3120 firmware by adjusting mux_ctrl_set_cfg() in datamux_ctrl.c to swap the switch positions.

My main concern is the DP0 and DP1 lanes. I notice that these are connected to Rx2 and Tx2 respectively. Is this OK? Or will we need to switch them to Rx1 and Tx1 for proper function?

I also have a question regarding the DisplayPort AUX lines. I found this in mux_ctrl_set_cfg():

/*

* Configure AUX1/2 resistor pull up/down based on DP configuration.

* If DP Config:

* AUX1 : 470K pull down

* AUX2 : 4.7M pull down

*

* If Non - DP Config:

* AUX1 : 1M pull up

* AUX2 : 1M pull down

*/

if (dp_sink_get_pin_config () == DP_DFP_D_CONFIG_E)

{

aux_resistor_configure (AUX_1_470K_PD_RESISTOR, AUX_2_4P7MEG_PD_RESISTOR);

}

else

{

aux_resistor_configure (AUX_1_1MEG_PU_RESISTOR, AUX_2_1MEG_PD_RESISTOR);

}

If I'm not mistaken, shouldn't this be the opposite of the comment? Going by the VESA standard for DisplayPort, it looks like we want the Sink side to have 1M PU/PD on AUXP and AUXN respectively:

We actually have these 1M resistors populated external to the CYPD3120, so we have the firmware configured for no internal PU/PD:

aux_resistor_configure (AUX_NO_RESISTOR, AUX_NO_RESISTOR);

This seems to work (the AUX+ and AUX- signals look to be within spec) but I wanted to clarify the firmware comments above and make sure I'm understanding correctly.

Any thoughts are greatly appreciated!

Thanks!

[EDIT]

One more question, would having a USB-C receptacle rather than a plug require use of a Demux such as a TUSB564 on the UFP? Or would a mux on the DFP be sufficient to put the DP lanes in the correct orientation for the config on the UFP?

Show LessPSoC 4.2 connecting miniprog

Option external with reset not working

Reset option not working recognise GCC3PA recognize cortex MO

Where I could find info about external option?

Show Lesswhen debug mode is operate evrey thing ok until press start run

just-in-time (JIT) debugging instead of this dialog box

how could i fix it ? re install psoc creator ? what meaning of the msg error

see attached txt and image file please advice

Show LessCY4533 BRC Evaluation kit

Doc #: 630-60538-01

Sheet: 5

Section: B4

Pins: MH1, MH2, MH3, MH4

are these pins actually the case pins?

Want to verify before I continue.

Show Lessit possible require ccg3pa with 128 kb flash ?

I want to use BCR(CYPD3177) to get 9V power from power bank, and I don't have the SOC or MCU to communicate with BCR,

can I get the 9V voltage only by adjusting the external resistance?

The BCR has a HPI Specification, If I don't control the BCR by HPI, I think BCR has the default configurations,

but I can't find the default configurations in HPI Specification,how should I know the default configurations of BCR?

Show LessI'm using the SDK CYPD3171-24LQXQ_pb, and when Power Bank work under sink mode, does it support PD3.0 or not?

Why in EZ-PD Configuration Utility Sink Settings only BC1.2 and Apple charger are supported?How could I add other protocols like PD or QC?

And I used my board with the SDK CYPD3171-24LQXQ_pb, it works in sink mode, and the side of power source supports PD3.0 and QC3.0, why my board only get 9V VBUS from the power source and I changed the Sink PDO as 12V but will not get 12V, how can I get the 12V from the power source?