SRAM Forum Discussions

Hello

I need your help to find my SRAM componnent in ordre to change it with another compatibility pin to pin and the same functionnalities.

If I understood your document PRODUCT CHANGE NOTIFICATION " PCN155107" I can use this choose:

Part Number Old: CY7C1041D-10ZSXI

Part number New component: CY7C1041GN-10ZSXI if it is confirmatory on your part, I thank you for replying me on the subject by yes or by no.

Thank you very mutch.

Dear Mrs, Mr,

I would like to know if the SRAM reference's below from Cypress are strictly the same since the acquirement by Infineon (no change of technology and no change of technical parameters) :

- CY7C1062GE30-10BGXI or CY7C1062GE30-10BGXIT

- CY7C1371KVE33-100AXI

Many thanks in advance for your strong support

Best Regards

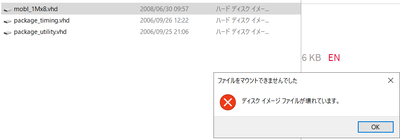

About the simulation model of CY62158ELL-45ZSXI I had the following VHDL, but is it possible to simulate with IBIS?

If possible, I would like to receive materials etc.

Show Less

The customer wanted to use the IBIS model for SI analysis, so I was irritated to ask for materials.

Isn't it wrong with the following file?

Also, I get the following error, can you figure out the cause?

Show Less

Hi

We are using the CY7C4122KV13/CY7C4142KV13 SRAM in our design, with the address parity logic enabled. For the same:

1) We need the switching characteristics and Switching Waveforms for Address Parity and Parity Error operations as they were not available in the product datasheet.

2) Also, I have a two part query I'll illustrated with an example. Suppose we initiated a transaction T0 and within the RL cycles of T0, we initiate two more transactions T1 and T2. After RL cycles, we receive a Parity Error for T0. Then:

a) if the parity error counter indicates there was only 1 error and after clearing the parity error, should all the transactions. i.e. T0, T1 and T2 need to be repeated or only the first transaction (T0).

b) related to this, if the parity error counter indicates there were 2 errors, does this imply that the first 2 consecutive transactions (T0 and T1) failed or can it be T0 and T2?

It would be ideal if a dedicated documentation for the address parity implementation is available.

Regards

Aman

HI All

I'd like to confirm whether CY62147GN30-45BVXI can support dual CE.

Ordering Code Definition shows 62417"2" can support Dual CE.

CY62147GN30 does not have "2". So I think that this parts# can not support dual CE.

But data sheet shows CY62147GN30-45BVXIT can support dual CE even if "Chip Enable : X = Blank."

Could you please tell me whether CY62147GN30-45BVXI can support dual CE?

Best regards

Show Less

I have already seen "SRAM Board Design Guidelines (Whitepaper)" document and it does not provide any information about length matching.

I am aware that I need to use length matching so that bad data is not sampled while reading or miswriting. But I can't find any documentation or information about what the length matching will be as a unit of time.

- Is it any need for length matching in the PCB layout when using these SRAM's?

Thanks and Regards,

Hi, I'm using the CY14V101QS (16 Pin) 1Mbit QSPI SRAM. On power up, by default in which mode is it coming up ?

I wanted to confirm if it does indeed come up in SPI (MOSI, MISO, CSB, SCK) configuration by default on power up, or does it move to QSPI without first writing some register in SPI.

if indeed a reg write is required, can this be saved/flashed ?

Or is it that always on power up, you communicate through SPI, write a register and then move to QSPI ?

We are using a CY7C1645KV18-400BZXI QDR-II+ for one of our designs with an 1.8V I/O supply, which is supported as clearly stated in the Datasheet.

We discovered that the Xilinx IP for the QDRII doesn’t support 1.8V. We asked for a solution and Xilinx proposed a workaround that would permit us to generate a bitstream with 1.8V I/O and it still didn’t work.

Is there another Soft IP by Infineon that we could use to drive our QDRII+? Or another way to generate a bitstream for 1.8V I/O?

Show Less

Hi,

When did you start mass production shipment of CY7C1051H30?

Thanks and regards,