- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I believe there are errors in the datasheet for P/N CY7C1380D. Please check

the following issues:

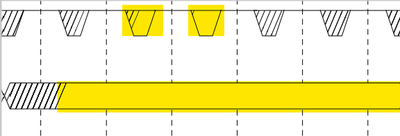

1. The timing diagrams on pages 24 and on are visually corrupted. The hatching used

to indicated don't care is only partially visible which makes the diagram confusing.

2. The "Functional overview" section describes the various access patterns for using the device.

However, the descriptions don't match up with the waveforms (even disregarding the visual issues).

For example, the description of "Single Read Accesses" asserts that during the first cycle of an ADSP_N read, the write signals GW_n/BWE_n must be deasserted. But the diagram marks them as Don't Care.

I compared both the diagram and the description to a newer datasheet for P/N CY7C1381KV33

and neither problem appears there. I believe that in (2) above the datasheet verbal description is wrong (indeed, it does not match the one in CY7C1381KV33). And the corrupted diagram seems

to be identical to the one in the newer datasheet, except for the missing hatched lines.

I've been unable to contact support so I'm hoping they keep an eye on reports via this channel.

Regards,

John

Solved! Go to Solution.

- Tags:

- datasheet-error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @locrauteiyelu-7,

1) Yes, that needs to be corrected. The yellow highlighted area is the don't care region.

2) If ADSP# is asserted, the SRAM always initiates a read cycle regardless of the state of GW, BWE, or BWX. Please refer to footnote#9 (pg#10).

Thanks,

Ritwick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @locrauteiyelu-7,

1) Yes, that needs to be corrected. The yellow highlighted area is the don't care region.

2) If ADSP# is asserted, the SRAM always initiates a read cycle regardless of the state of GW, BWE, or BWX. Please refer to footnote#9 (pg#10).

Thanks,

Ritwick