PSoC™ 6 Forum Discussions

Hi all,

I am using the PSoC 6 cy8ckit-064b0s2-4343w . I attempted to construct a UART interrupt in Modustoolbox using SCB blocks without FreeRTOS, and the hardware interrupt happened at that time. However, when I implemented it again with FreeRTOS, I did not encounter a hardware interrupt since FreeRTOS does not call the interrupt function while transmitting.

Show LessDear Community

We are developing 3 Models in 1 product.

for convenience, I want to define a MACRO in the Modus IDE with common code for 3 models.

How to define MACRO in the Modus IDE.

For eg:

If revise the MACRO = MODEL_1,

We can compile the code which is in #if (MODEL == MODEL_1).

If revise the MACRO = MODEL_2,

We can compile the code which is in #if (MODEL == MODEL_2).

If revise the MACRO = MODEL_3,

We can compile the code which is in #if (MODEL == MODEL_3).

Best regards.

Show LessHi all experts

I use PSoC62 EVK (CY8CKIT-062S2) to develop communication functions,IDE is mtb3.0

BSP package is CY8C624ABZI-S2D44

and use an oscilloscope to verify functionalityI develop through the example of HAL_SPI_Master

Initialize SPI using HAL API

Then I found a problem,If I modify the BSP package to (CY8C6248BZI-S2D44)use the BSP Assistant

The final product is QFN (LQI) package

SCB1, 2, 5 are all normal when I use BZI

Then it is normal to use 1 and 2 when LQI

but! As long as the SPI_send of SCB 5 is added to the BSP project of LQI, the MCU will be stuck

and I use LQI packaged chips to run BZI's BSP project and it can be used normally!

Finally, I tested the LQI package Chip to run on the LQI project, and there will be the same problem that SCB5 cannot SPI_send

So I would like to ask how to correctly use SCB5-related communication on LQI chips and projects

i am working on USB-UART echo, and i dont wish to provide the cy_retarget_io_init() with my RX and TX pins, as i wish to use them for some other purpose. can i do that?

and if i comment the cy_retarget_io_init() then the program gets terminated before completion.

and how can i set the baudrate of the UART in it?

Show LessHi,

I used psoc programmer to burn the hex files on to the poc 4 devices.

Do we have something similar tool for Psoc6 Hex file.

Let me know using JTAG how can I burn the HEX files on to flash.

Show LessHi,

I am trying trying to implement a signal where I have 2 timer and I just send a single pulse for each bit.

To implement I was just trying with 2 pwm in a single thread.

I get the following error as soon as I try to start the PMW.

Can some one guide me what can be wrong on executing rslt = cyhal_pwm_start(&pwm_obj1); ?

Show Less

We are running into a program not being able to connect to a CY8C624AAZI-S2D44 on a new PCB we have recently used the CY8C624AAZI-S2D14 and did not have any issues. Both devices are setup the same hardware wise using a Miniprog4 and cypress programmer. From what we know the only difference between the two devices is the crypto accelerator. Can anyone provide any insight why we are unable to connect to the S2D44 version? Does the .hex file have anything to do with the connection steps?

Show Less

Where can I get errata for PsoC CY8C6347FMI? I've searched the Infineon website without any luck. I did notice this post: https://community.infineon.com/t5/PSoC-6/Where-can-errata-be-found-for-PSoC-6-die-revs/td-p/324797 Where the errata was obtained from a local FAE. But I'd really just like to download the errata sheet and get on with my project.

Dean

Show LessDear Sirs,

Just like Bernadett, I'm looking for

-Maximum soldering temperature

-How long can the product be exposed to the maximum soldering temperature.

for the following products:

Manufacturer: Infineon

Manufacturer code: TC275TP64F200WDCKXUMA1

and TLF35584QVVS1XUMA2

(I would need this info for AUDIT by automotive project)

Thanks in advance!

kind regards

Show LessHi all,

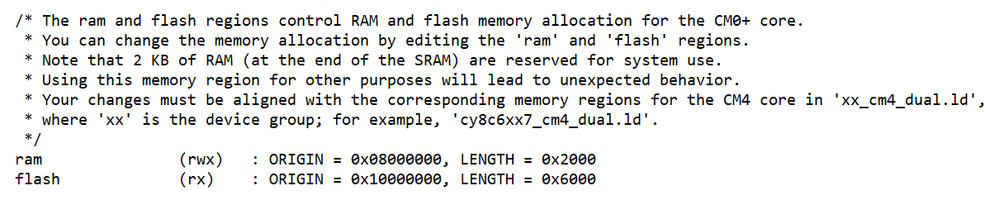

I'm trying to add freeRTOS to cm0p for the project "Dual-CPU_Empty_PSoC6_App" but I keep getting this error:

../bsps/TARGET_APP_CY8CPROTO-062-4343W/COMPONENT_CM0P/TOOLCHAIN_GCC_ARM/linker.ld:312 cannot move location counter backwards (from 08001670 to 08001000)

I'm pretty new using both PSoC62 and freeRTOS. I'm able to add freeRTOS to cm4 but I need freeRTOS in each core. The error seems related to RAM but I can't figure what's wrong. Below are pictures showing the linker files settings for the RAM for both cores:

Is this a setting I need to change in FreeRTOSConfig.h or something else?

Thanks

Show Less