- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a problem implementing a SPI slave on a PSoC 6 device (CYBLE-416045-02). I have an interrupt routine on the Rx FIFO Not Empty event. It is working fine receiving data from the master. The problem is that when sending data back to the master, the bytes placed into the TX FIFO occur on MISO one byte later than expected.

I am clearing the TX FIFO at the beginning of a SPI frame using an interrupt on the SS line. Then, at the SPI interrupt after receiving the first byte, I place a byte into the TX FIFO (using Cy_SCB_SPI_Write) and expect that byte to appear on MISO when the next byte is clocked by the master, but it does not appear then, it only appears on the byte following the next one.

Attached is the code, and also an analyzer trace. Note that I am outputting some additional debug signals on spare pins to show when events are occurring.

I have tried many combinations of API calls to clear the FIFO at different times but nothing seems to fix this problem. I have also tried slowing down the clock from the master, which also increases the inter-byte spacing, but that also makes no difference. I have seen in other posts some talk of there being some inherent delay with writes to the TX FIFO, but I cannot find any hard information on this.

Any help with this would be very much appreciated.

Peter

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

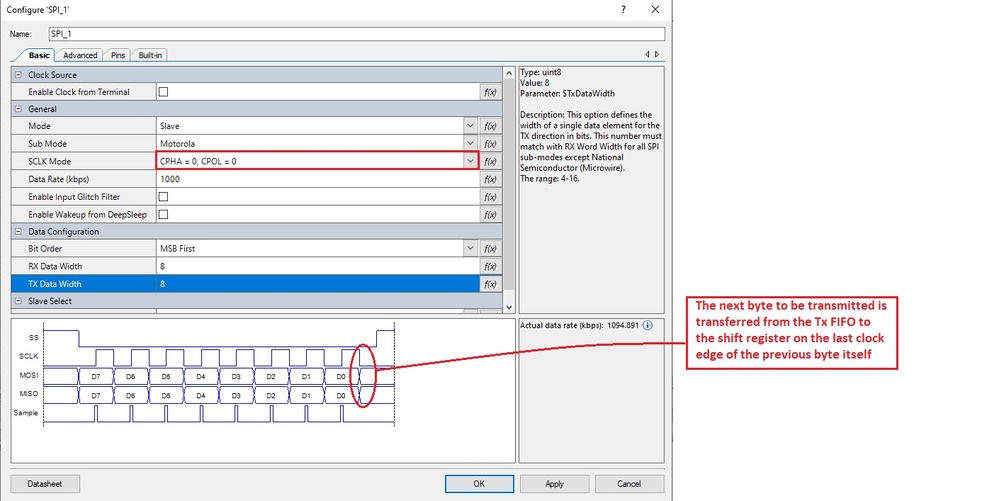

If you are using the default Mode 0(CPHA=0,CPOL=0) of SPI, then this behavior is probably occurring because the next byte to be sent out by the SPI slave is already loaded on the last clock edge (falling edge) of the previous byte itself. Below is a screenshot of the SPI component timing diagram that shows this:

So, in your case, the data is loaded in the last clock edge when the address byte is transmitted itself.

To overcome this, would it be possible to try:

1) Loading the Tx FIFO with data on or before the address byte(first byte) transmission from the master ?

But if this does not satisfy your application requirement(where the response data is decided only after the first address byte), then can you try:

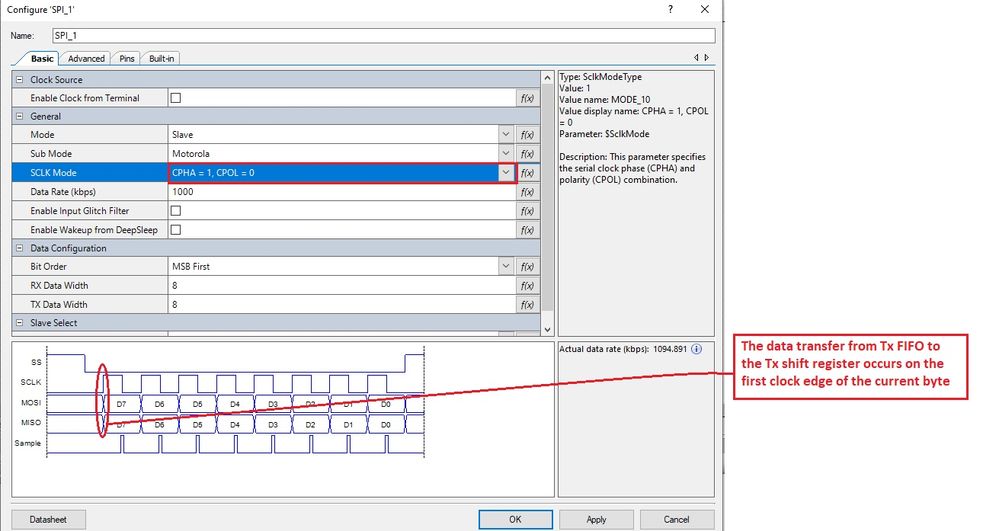

2) Changing the SPI SCLK mode to Mode 1(CPHA=1,CPOL=0). In this mode, the loading of the shift register seems to happen only the first clock edge of the current byte, as shown in the below screenshot:

But note that the SPI master also has to be changed to this mode.

3) Or (on the SPI master's side) try lifting up the SPI SS after the first address byte, and lowering it before the next response byte (in between which you can load the slave response byte into the Tx FIFO).

Best Regards,

Prem Sai