- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

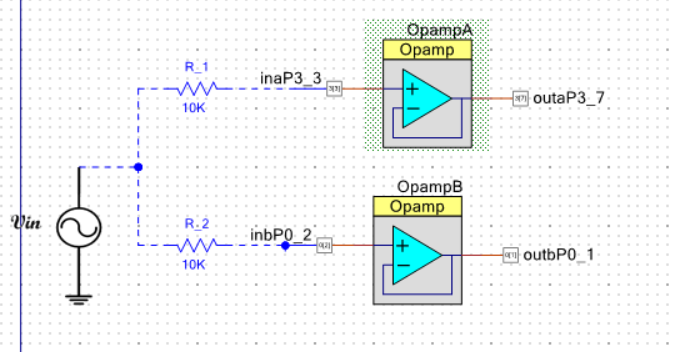

Using two op-amps as voltage followers, one of them does not load the input signal, the other one does- see the figure below.

The signal at inaP3_3 (port P3[3] ) is fine, no problem. But at inbP0_2 (port P0[2]) , the AC component is removed and I only have the DC portion of Vin (1kHz, 0.5Vpp with 0.3V DC offset). At lower frequencies I start to see more AC component. As if there's a cap on the input.

I'm using the CY8Ckit-059, so I checked the schematic and did not see anything connected to this pin.

Can anyone suggest how this could be happening?

Solved! Go to Solution.

- Labels:

-

ispn:39618:1:0

-

l1:314:1:0

-

PSoC5LP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems it was already:

If you have CY8CKIT-059 and you have not deleted C12 (P0.2) then this is the problem.

look here: https://community.cypress.com/thread/12559

You will have to either delete or use another contact.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If I change input from P0[2] to P0[6] , then everything it works fine. However, the analog routing is much longer. Choosing P0[2] makes more sense since it is close to the + input of OpampB (corresponding to OPAMP0 in hardware)

So there's an issue with P0[2].

Note: If I delete the pin and drag a new pin over without choosing a port, then the software automatically chooses P0[2] anyway.

Hope someone can enlighten me

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm sorry but this may not be an answer, but as the issue seemed to be interesting, I ran some tests by myself, too.

With the original using P0[2] scenario, when I set the frequency of the input signal to 10Hz, both output seemed to be OK.

Then as I changed the input frequency to higher, 100Hz, 1kHz, channel B output decreased much faster than channel A.

So I think that the connecting pattern of P0[2] to OpAmp0 may be physically composing a low-pass filter,

but the connecting pattern of P0[6] to OpAmp0's cut-off is much higher.

In the following pictures, ch1 is chA OpAmp3, ch2 is chB OpAmp0

(1) Input 10Hz 0.5v pp + 0.3V DC

(2) Input 100Hz

(3) Input 1kHz

Then I changed the chB input to P0[6]

(4) Input 10Hz

(5) Input 100Hz

(6) Input 1kHz

Analog pattern of OpAmp3

Analog pattern of OpAmp0 with P0[2]

Analog pattern of OpAmp0 with P0[6]

In this case as you had 2 channels, you could notice the problem,

but I wonder if I encounter this with only 1 channel without anything to compare,

how could I notice the issue..

moto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems it was already:

If you have CY8CKIT-059 and you have not deleted C12 (P0.2) then this is the problem.

look here: https://community.cypress.com/thread/12559

You will have to either delete or use another contact.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Evgeniy-san,

Thank you for the information.

I should have checked the schematic... I was only thinking of the PSoC internal circuit.

Having C12 attached, surely make it a low pass!

So probably the most affordable answer is to use a port without C attached, such as P0[6] 😉

Best Regards,

5-Feb-2019

Motoo Tanaka

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That's excellent- I did check the schematic and did not see a cap there, that's why I started this thread. But if I scroll down the data sheet a little: right in plain sight !!