- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to use a psoc5 or psoc5lp to build a programmable current mode pwm controller for a switching regulator. I have a freesoc and a freesoc mini that I can use for prototyping, so my preference is psoc creator 2.2, sp1, but if that is too limiting, then I can switch to a cyc8kit, and a later version of psoc creator.

This is a standard buck regulator configuration. The primary switching element is a MOSFET. There is a current sense resistor after the inductor to measure inductor current. The current sense voltage is amplified by an external opamp (due to the large voltages involved).

Please note that resistor, inductor, and capacitor values have not been calculated yet; those components are placeholders.

This will be a standard double-loop current mode supply:

- Each cycle is initiated by a free-running clock.

- The clock sets a RS flipflop. (NOTE: the schematic above needs an edge-detector)

- When the flipflop is set, the gate of Q3 is driven high, which turns on Q2 and starts current flowing through L1

- U3 measures the current through L1 using sense resistor R1 and feeds that back into the PSoC to Comp_1.

- When Comp1 goes low, it resets the RS flipflop, turning off Q3 and Q2.

- The positive input to Comp_1 comes from a VDAC

- To close the outer feedback loop, the output voltage is measured by R10 and R11 and fed into a SAR ADC.

Here is the part I haven't implmented. I want to take the output from the SAR ADC, subtract it from a setpoint, then load that into a down-counter in order to implement slope compensation. The output of the down-counter should be the input to the VDAC.

- The setpoint comes from a data register

- The setpoint is compared with a measured value to obtain the error value (subtractor)

- The error value is decremented gradually to implement slope compensation (down counter)

- The error value is sent to a VDAC

I have not been able to work out how to:

- Get the raw output from the SAR ADC

- Create a CPU-accessible data register

- Subtract the raw output from the data register

- Load the result into a counter

- Supply the counter output to the VDAC

Now, I know that I can implement these functions in Verilog very easily, but I don't think that the compiler will produce code that uses the UDBs. How can I build this in PSoC Creator? I'm certain that this is all doable with UDBs and it must be very similar to implementing an all-hardware PID loop. I want to fit 4 of these controllers into one PSoC so getting it to work with UDBs is important.

Is it doable with PSoC creator 2.2 SP1? Or do I need to switch to a later version for more control over UDBs and buy a new PSoC 5LP development platform?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Out of tasks #1-5, only #3 (subtract) and #4 (count down) require hardware resources. Implemented in Verilog, 8-bit configuration will consume about 5% of macrocells only, so there should be no problem to do it in Verilog entirely.

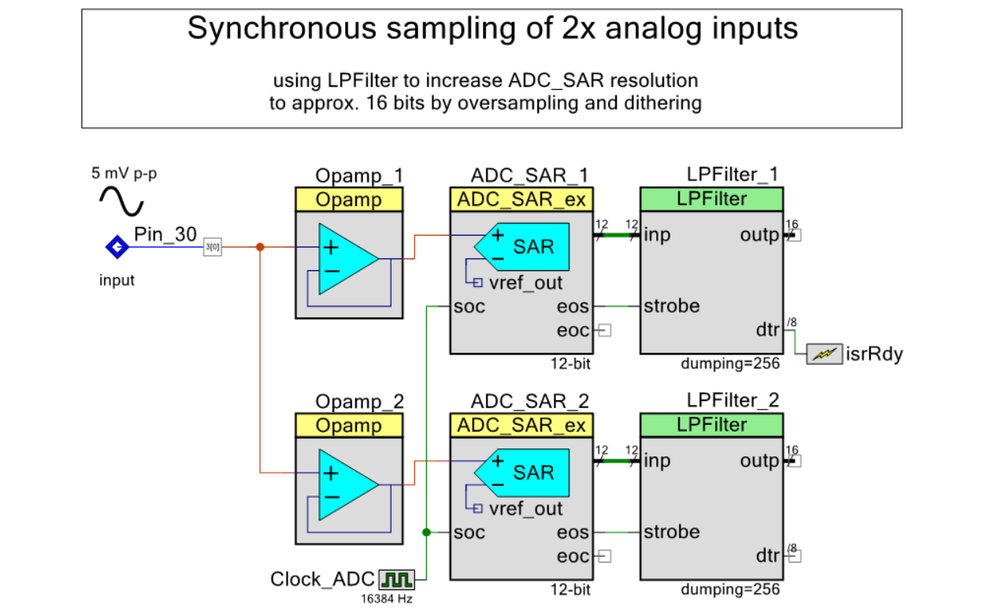

To get acces to the ADC_SAR raw data use modified ADC component with digital output bus

Re: ADC Direct Digital Output - Route to UDB/Logic

The above project also has LPFilter component, which "may" serve as a substitute for a counter (at least for some testing).

The example of instantiating CPU-accessible ControlReg in Verilog can be found here:

http://www.cypress.com/comment/392376#comment-392376

FreeSoc and FreeMini are excellent boards and work with latest Creator (v4.2). The v4.2 can read files from older versions, but v4.0 and below can not read 4.2. I use mostly 4.0 for that reason. You may consider also KIT-059, which is comparable with FreeMini (once it blows up).

Please share your results with the community.

/odissey1