- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

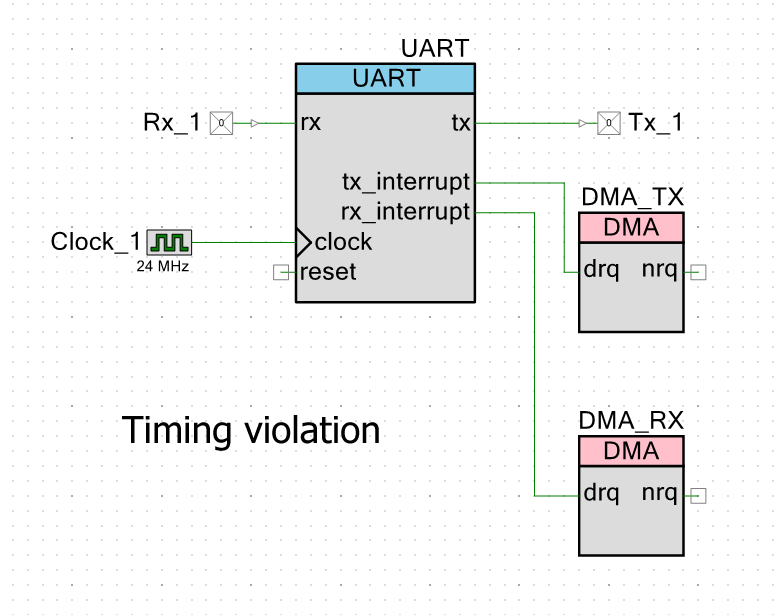

How can I use a UART on a PSoC5LP at 3Mbps with DMA?

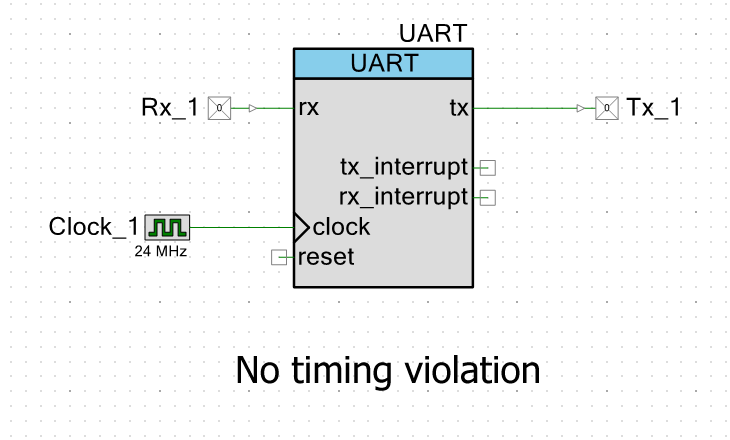

If I use a UART with a 24MHz input clock and 8x oversampling, everything is fine.

If I now connect two DMA components to it, I get setup time violations.

I have already tried reducing the temperature range.

Is there any way to make this work?

Can I ignore the warning if I know that my actual temperature range will be 25ºC ± 10ºC

Hugo

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hugo,

I've tested your configuration shown above. With BUS_CLK = 3MHz

I get warnings but NO TIMING VIOLATIONS.

Can you include a minimized archive of your project?

Something in your configuration is missing.

Len

"Engineering is an Art. The Art of Compromise."

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have set the clocks as shown in this image:

I tried setting the BUS_CLK to 3MHz, but that still produces a timing violation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hugo,

Try adding a Sync component after isr.

/odissey1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you so much. This fixed it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hugo,

The main issue is that the UART component has internal logic connections not seen from the outside that have the BUS_CLK routing to it. The Static Timing analysis complaining about the setup violations are taking BUS_CLK timing into account. Having said that, your BUS_CLK is set to 64MHz which means that a clock period is only 15.6ns. However, due to the static routing delays of the clocks, the maximum BUS_CLK you can support without setup violations is 47.9MHz. See the file "Design01_timing.html". However, changing the PLL to 47.9 MHz still doesn't fix it.

I've included a modified version of your circuit that runs at 39MHz BUS_CLK. No violations. See if this will work for you.

Len

"Engineering is an Art. The Art of Compromise."