- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

My customer use CapSense.

Customers are concerned about flat spots as they tune.

Why do flat spots occur in CapSesnse?

I understand it can be solved by using PRS as the clock source.

Is there a case where PRS cannot be selected?

Best Regards.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi taas_3144281,

Flat spots occur due to the inherent nature of the CSD sigma delta converter. This creates certain non - sensitive regions in the Capacitance to digital count conversion. It is experimentally found that, these regions specifically occur at 25 %, 50 %, 75 %. The width and magnitude of the flat spots depend on the ratio of Fmod/ Fsw and Cmod / Cs.

PRS is the best option to eliminate flat spots since it changes the Fsw value every cycle and makes sure that the CSD converter doesn't get locked up at a particular rawcount.

Also, setting the baseline at 85 % using IDAC auto - calibration or changing IDAC manually so that we do not hit one of these regions helps in avoiding flat spots.

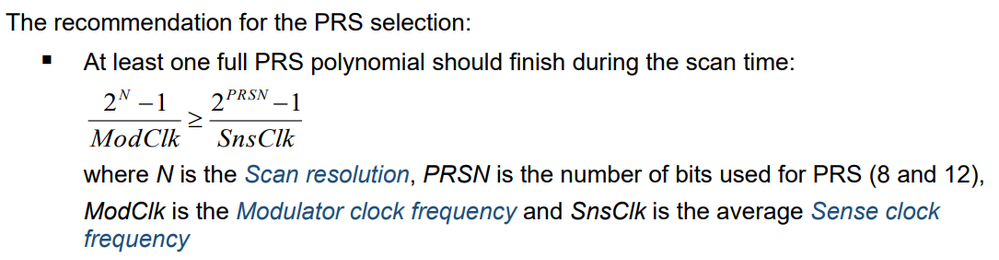

PRS can not be used if the following equation is not satisfied.

In other words, set your ModClk, Sense Clk and Resolution such that you can use PRS to avoid flat spots.

Regards,

Bragadeesh

Bragadeesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi taas_3144281,

Flat spots occur due to the inherent nature of the CSD sigma delta converter. This creates certain non - sensitive regions in the Capacitance to digital count conversion. It is experimentally found that, these regions specifically occur at 25 %, 50 %, 75 %. The width and magnitude of the flat spots depend on the ratio of Fmod/ Fsw and Cmod / Cs.

PRS is the best option to eliminate flat spots since it changes the Fsw value every cycle and makes sure that the CSD converter doesn't get locked up at a particular rawcount.

Also, setting the baseline at 85 % using IDAC auto - calibration or changing IDAC manually so that we do not hit one of these regions helps in avoiding flat spots.

PRS can not be used if the following equation is not satisfied.

In other words, set your ModClk, Sense Clk and Resolution such that you can use PRS to avoid flat spots.

Regards,

Bragadeesh

Bragadeesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Bragadeesh-san

Thank you for your answer.

I understand that PRS can be used if Tscan ≥ Tprs.

For example, can PRS be used with the following parameter settings?

ModClk : 24000kHz

Sense clock source : PRS8

Sense Clk : 3000kHz

Resolution : 12bit

Tscan=171μs

Tprs=85μs

Even if the baseline is set to 60% or 70% by using PRS, is it not affected by the flat spots?

My customer is concerned that if the baseline is set to 85%, the raw count value may saturate when touching the sensor.

Best Regards,

Asanuma

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi taas_3144281,

Yes, PRS can be used in the above configuration you mentioned. Yes, the customer can set calibration level to 60 or 70 % when using PRS since flat spots are reduced.

Additionally see Setting CapSense Parameters for Designs with Temperature, Humidity, and other Gradual Environmental ...

Regards,

Bragadeesh

Bragadeesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Bragadeesh-san

Thank you for your answer.

Best Regards,

Asanuma