- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

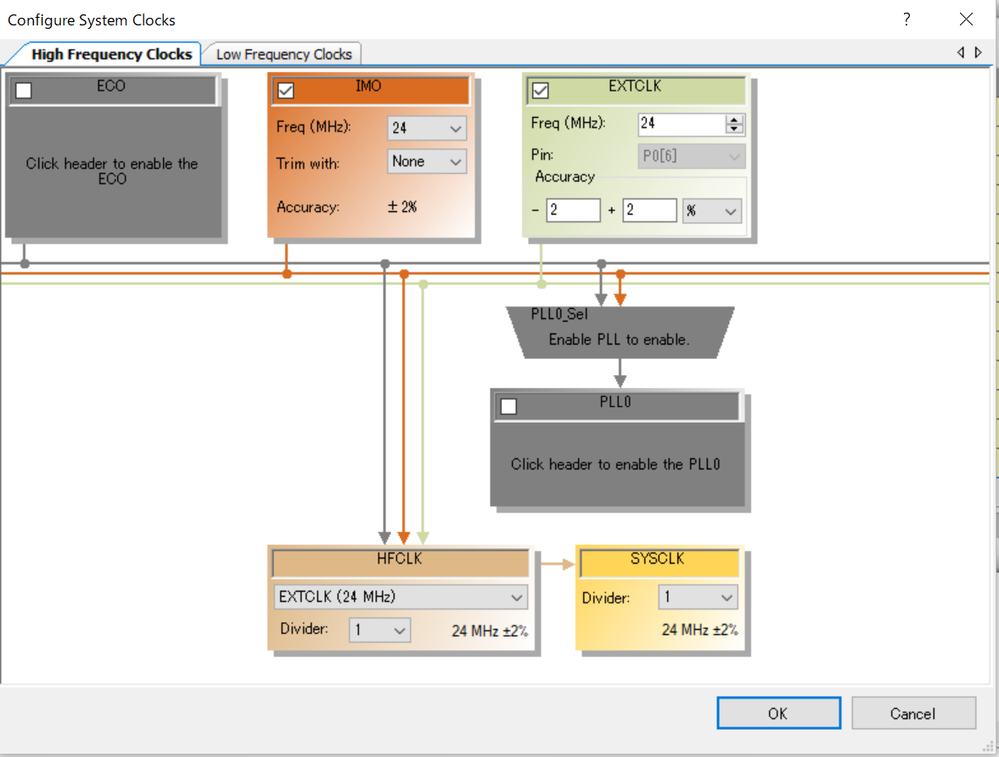

In order to operate PSoC4S with an external clock,

Enabled EXTCLK of Configure System Clocks.

Frequency is 24MHz

Accuracy is -2% to + 2%.

HFCLK set to EXTCKL

No error occurs after Build.

The clock of the SG-8002CE24MHSTB-L3 oscillator is input to P0 [6].

However, PSoC4 does not start after programming.

Are there any restrictions on how to use an external clock?

For example, are there any application notes listed?

Regards,

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Masashi,

The device always starts up using the IMO and the external clock must be enabled in user mode; so the device cannot be started from a reset, which is clocked by the external clock. When manually configuring a pin as the input to the EXTCLK, the drive mode of the pin must be set to high-impedance digital to enable the digital input buffer.

Please refer to the External Clock(EXTCLK) section in the Architecture TRM for PSoC 4100S for more details on this: https://www.cypress.com/file/280681/download

Best Regards

Ekta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Additional information.

If EXTCLK is disabled and set to IMO, it operates normally.

Is there a relationship between the power-on sequence and the timing at which the external clock becomes valid?

?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Masashi,

The device always starts up using the IMO and the external clock must be enabled in user mode; so the device cannot be started from a reset, which is clocked by the external clock. When manually configuring a pin as the input to the EXTCLK, the drive mode of the pin must be set to high-impedance digital to enable the digital input buffer.

Please refer to the External Clock(EXTCLK) section in the Architecture TRM for PSoC 4100S for more details on this: https://www.cypress.com/file/280681/download

Best Regards

Ekta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ekta-san,

thank you for your answer.

We understand that there is also a description of the API in the system guide.

However We think that waiting time until the main clock changes is stable is important.

Do you have application notes or sample code?

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Masashi-san,

At present we do not have any application note on external clock for psoc 4100s device.

As per my understanding you are using API CySysClkWriteHfclkDirect (uint32 clkSelect) to change the clock source from IMO to EXTCLK after the device starts.

The clock source will change to ExtClk from the next cycle onwards as soon as the API for the change of HFCLK source from IMO to EXTCLK is executed.

Best Regards

Ekta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ekta-san,

Thank you for your supoort.

We understood this issue.

I will try to change clock using the API.

I look forward to the release of the application note.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ekta-san,

/* Clock Settings */

IMO : 24MHz

EXTCLK : 24MHz

Initial setting of HFCLK is IMO(24MHz)

After PSoC starts, the clock is switched with the following API.

/* Clock Change Code */

CySysFlashSetWaitCycles(24u);

CySysClkWriteHfclkDirect(CY_SYS_CLK_HFCLK_EXTCLK);

PSoC operation stops at the timing of clock changing.

Are there any necessary conditions for changing clocks?

Is a delay required for the clock to stabilize after the change is made?

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As we confirmed, even PSoC4 does not work depending on the series.

PSoC4S has confirmed the operation of changing clock.

However, it does not work with PSoC4S +.

PSoC4S : CY8CKIT-149

PSoC4S+ : CY8CKIT-145

Both of them have the same project contents and input the external clock to P0[6].

Is there any necessary steps to switch clocks?

Attach a simple project.

Please could you confirm it?

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Masashi,

I tried progrmming both PSoC 4000S and PSoC 4100S PLUS with the project provided by you.

I was able to recreated the issue mentioned by you.

The Extclk switching was working fine with the PSoC 4000S device. However, it is not working with 4000S plus device.

I will update on this thread once the issue is resolved.

Best Regards

Ekta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Masashi-San,

Please use the following code for switching clock to EXTCLK in case of PSoC 4100S Plus

#include "project.h"

int main(void)

{

CY_SET_REG32((void *)(CYREG_HSIOM_PORT_SEL0), (CYVAL_HSIOM_IO0_SEL_ACT_0 << (6 * 4))); /* HSIOM_IO0_SEL_ACT_0 */

CY_SET_REG32((void *)(CYREG_GPIO_PRT0_PC), (LED_DM_DIG_HIZ << (6 * 3))); /* High Impedance Digital */

/* 6 is a pin number, 3 and 4 are bitfield widths */

CySysClkWriteHfclkDirect(CY_SYS_CLK_HFCLK_EXTCLK);

for(;;)

{

LED_Write(0);

CyDelay(500);

LED_Write(1);

CyDelay(500);

}

}

I have attached the sample project below.

Best Regards

Ekta