- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

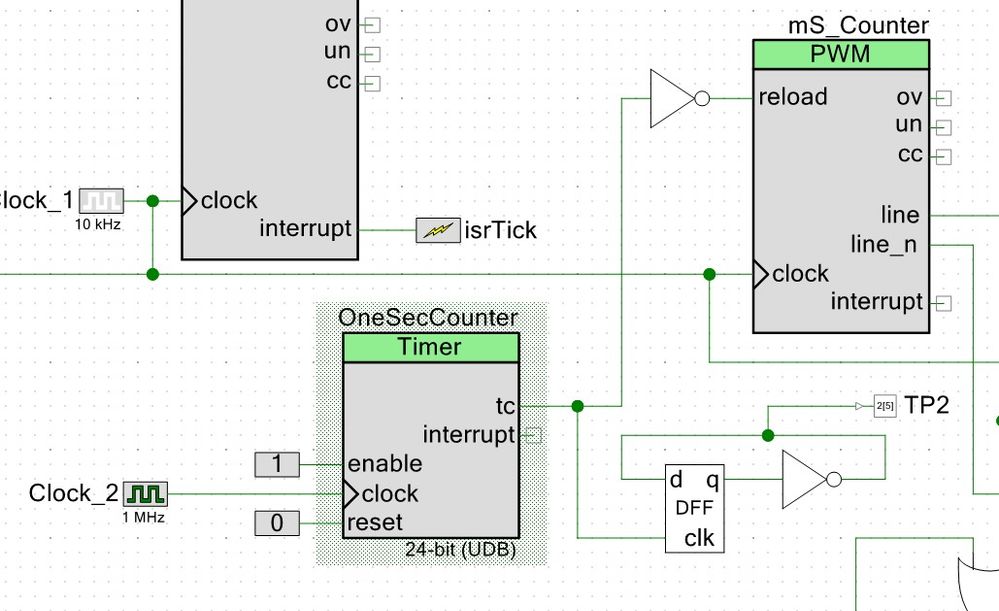

I am trying to create a Monostable of 300mS than is triggered every second. It was easy enough when I worked with a 16 bit counter because a PWM counter (ms_Counter) with a period of 10000 (with a clock of 10KHz) and a Compare setting of 3000 was the perfect solution. Unfortunately I needed greater resolution for the period and since the component can only be configured for 16 bits, I went to a 24bit counter with a clock of 1MHz and a Period of 1000000 (OneSecCounter)which generated 1 Hz. I tried to get it to trigger (using the reload pin) a PWM counter with a period of 65000 and the Compare remained at 3000. I tried to get the TC of the 24 bit counter to reload the PWM counter as you can see in the attached drawing, but the monostable pulse occurred at a far longer period, perhaps the 65000 which would suggest that the reload does not work the way I think. I also tried the period at 4000 and the output was much faster than the desired 1 second.

According to the datasheet "For all devices, except PSoC 4000, PSoC 4100, PSoC 4200, it should only be used when the counter is not running.", so it seems that I can activate the Reload when it is running. I found the following in the data sheet a little confusing "In up and up/down counting modes, the counter is initialized with “0” (for PSoC 4000, PSoC 4100, PSoC 4200 devices).". Does that mean the reload should be active low? I tried both ways but it made no difference .

In the schematic you can see a divide by 2 D-FF to prove that the OneSecCounter is working. I also include the register settings

Does anyone have any idea what I can do generate the monostable pulse? Any help would be much appreciated!

Solved! Go to Solution.

- Labels:

-

PSoC 4 MCU

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That one is not so obvious, but once you read the reason, you'll say, doh!

(I'm assuming you meant the RELOAD input, not the RESET input).

The RELOAD input is sampled with its own counter CLOCK input (10kHz) at the CLOCK rising edge.

The TC from the 1 second counter is driven by a 1MHz clock. Therefore, TC is active for just 1 clock cycle at 1MHz. The probability that TC is active just as a rising edge of 10kHz occurs, is pretty slim. Hence, the 300ms counter never gets reloaded.

Also, I just noticed there's an inverter in front of the RELOAD input. This would make the 300ms counter reload continuously. So, lose the invertor and my explanation holds up.

I hope that was clear enough to understand. If not, I can try again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You could use the Counter UDB component (24-bit) and use the "tc" and "comp" terminals to create your one-pulse signal. Basically set the signal on "comp" and clear on "tc". The period of the counter should match the 1 second and the compare value the 300 ms.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply.

I did try the configuration that you show, but it did not seem to count. I am not sure how your counter is configured, but I did try several settings, to no avail. From the data sheet, it appears to me that there needs to be a switching waveform on the count input.

I messed around with the counter component and in the end I did manage to get it to work the way I wanted even without the SR-FF., To start with I had a problem which is shown in the figure below. I wonder what the "official" solution to the inability to collect clock2. My solution was to use a D-FF to divide clock3 by 2 and feed that to the count input. Is there a better way?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

Good, you discovered how to make it work. Here are the reasons why the S-R FF circuit caused difficulties. That said, it's a starting point.

As you found, the Count input needs to be used to count clock cycles, not held at logic 1. And, the counter Reset input needs a logic 0 signal.

The S-R FF does not work when you use the Compare and count up. This one is wierd. TC and Comp are momentarily simultaneously true when TC occurs while the counter is re-loaded with 0. Since TC is connected to R input of S-R FF, it over rides the S input. But, after another clock cycle at the S-R FF, the S-R FF should re-sample its S input, but doesn't. Hence S-R FF never changes state. It's as if the S-R FF only detects a rising edge on its inputs and the rising edge of the S input is lost when R input resets it. At least, that's my theory (I could be wrong). Sorry if that sounded confusing.

edit: Figured it out. S-R FF is doing exactly what it should do. The issue with counting up is, S-R FF is SET but never RESET until the end of the 1 second period. Hence the Q output remains logic 1 for the entire 1 second duration (minus the 1 clock cycle that TC resets the S-R FF). So, S-R FF is operating as it should.

To make S-R FF work, configure the counter to Down Count and set Compare to Lessthan. However, as you discovered, you don't need to S-R FF if you take the output directly from the Comp signal. Now, the counter can be configured to count up or to count down. It always works and you have the choice of setting the 300ms pulse at the beginning of the 1 second period (Count Up), or at the end of the 1 second period (Count Down).

As for the Count input, it's unfortunate that a Clock component can not be used directly. This is one of the shortfalls of Creator. A Clock component can only be directly connected to a "Clock" input on a component. I have used the same work-around as you, a D-FF with inverter. In the past, I tried using the Sync component, and tried UDB Clock Enable component and that didn't work either.

Hope this sheds some light at the end of the tunnel.

Good luck with your project.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, my bad. The UDB implementation doesn't allow to count on level, only on edge. You can slightly modify to this:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. This all resolves my problem.

Out of interest, I would still like to know why I couldn't get the RESET input on a PWM module (my original question) to restart the count.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That one is not so obvious, but once you read the reason, you'll say, doh!

(I'm assuming you meant the RELOAD input, not the RESET input).

The RELOAD input is sampled with its own counter CLOCK input (10kHz) at the CLOCK rising edge.

The TC from the 1 second counter is driven by a 1MHz clock. Therefore, TC is active for just 1 clock cycle at 1MHz. The probability that TC is active just as a rising edge of 10kHz occurs, is pretty slim. Hence, the 300ms counter never gets reloaded.

Also, I just noticed there's an inverter in front of the RELOAD input. This would make the 300ms counter reload continuously. So, lose the invertor and my explanation holds up.

I hope that was clear enough to understand. If not, I can try again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks.