- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I added the official driver(V16.2.1) to ARM program.

First, I try to read chip ID, and return ID message like datasheet. Then I try to read addr 0x000000, and return 0xFF, to this step, everything seems fine. But when I try to erase/write data to addr 0x0000000, the reg of SR1V always 0xFF, and SR2V is 0x00. That show the chip is in busy state.

1. This is hardware connect. And SPI set is: CPOL = 0、CPHA = 0, CLK = 3MHZ.

2. This is code, just call the official driver.

3. This is the logic wave.

ID wave:

erase wave:

can u give some help about this

look forward to apply.

Solved! Go to Solution.

- Labels:

-

Serial NOR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

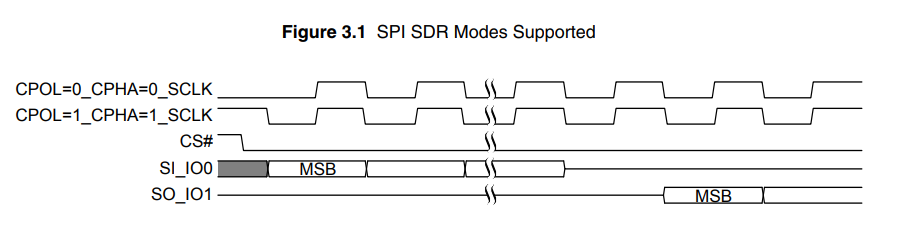

Could you please double check the SPI mode configured in your controller? Our device support only SPI modes 0 (CPOL = 0, CPHA = 0) and 3 (CPOL = 1, CPHA = 1). In both of these modes "input data into the device is always latched in on the rising edge of the SCK signal and the output data is always available from the falling edge of the SCK clock signal." So, the data on MOSI line should be stable at a clock rising edge. Please see the diagram from datasheet below. You can see that, data on MOSI line is stable during clock rising edge.

In your first response, you have mentioned that you are using CPOL = 0 and CPHA = 0 (SPI mode 0). I checked the waveform that you attached. The data on MOSI line is changing along with clock rising edge. So, I suspect the controller is not configured in SPI mode 0. Our device won't be able to decode data on MOSI line if it is changing along with rising edge of the clock. Please see the picture below.

So, please double check the SPI mode configured in your controller and test again.

I am not sure how FL128S device works without changing the settings. To get a better understanding, please provide waveform your SPI operations to FL128S also.

Thanks and Regards,

Sudheesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

To get a better understanding about this issue could you please use below slld function to perform erase operation?

- slld_RDSRCmd();

- slld_WRENCmd();

- slld_RDSRCmd();

- slld_SECmd();

- slld_Poll();

Please check the status register value in steps 1 and 3 and capture waveform above sequence of functions.

Can you provide your slld source code? We can review it and provide our comments.

Thanks and Regards,

Sudheesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I modified the code according to your steps, and debuged.

In step 1 and 3, the reg are all 0xFF. Here are the captured waveforms.

SLLD_STATUS slld_SEOp

(

BYTE device_num, /* device number */

ADDRESS sys_addr, /* device address given by system */

DEVSTATUS *dev_status_ptr /* variable to store device status */

)

{

SLLD_STATUS status = SLLD_OK;

BYTE poll_data;

status = slld_RDSRCmd(device_num, &poll_data); /* test line */

status = slld_WRENCmd(device_num);

if(status != SLLD_OK)

return(status);

status = slld_RDSRCmd(device_num, &poll_data); /* test line */

status = slld_SECmd(device_num, sys_addr);

if(status != SLLD_OK)

return(status);

status = slld_Poll(device_num, dev_status_ptr); /* loop in here */

if(status != SLLD_OK)

return(status);

status = slld_WRDICmd(device_num); /* just in case SEOp is operated on a protected area */

return(status);

}

This is the function that I'm calling, and add the code of line 11 and 17 to test setp 1 and 3. The more detailed code about SL DRIVE is attached.

Are there any initialization steps required ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I replaced the SL256L with the SL128S. And the op of read ID, erase, write, and read, it's worked. I'm not chang my code anymore.

But the SLLD_DRIVER is for SL256L, amazing. The instructions are compatible, but why op(erase/write) in SL256L was failed. (I try in other board, also filed).

Pls verify code works on your chip.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you please double check the SPI mode configured in your controller? Our device support only SPI modes 0 (CPOL = 0, CPHA = 0) and 3 (CPOL = 1, CPHA = 1). In both of these modes "input data into the device is always latched in on the rising edge of the SCK signal and the output data is always available from the falling edge of the SCK clock signal." So, the data on MOSI line should be stable at a clock rising edge. Please see the diagram from datasheet below. You can see that, data on MOSI line is stable during clock rising edge.

In your first response, you have mentioned that you are using CPOL = 0 and CPHA = 0 (SPI mode 0). I checked the waveform that you attached. The data on MOSI line is changing along with clock rising edge. So, I suspect the controller is not configured in SPI mode 0. Our device won't be able to decode data on MOSI line if it is changing along with rising edge of the clock. Please see the picture below.

So, please double check the SPI mode configured in your controller and test again.

I am not sure how FL128S device works without changing the settings. To get a better understanding, please provide waveform your SPI operations to FL128S also.

Thanks and Regards,

Sudheesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for you reply. I read datasheet of ARM chip again, found that ARM's SPI mode 0, it's not consistent with the general Settings.

And I changed the mode set(ARM's SPI CPOL = 1 and CPHA = 0), SL25FL256L could worked. Here is the ARM(TMS570LS3137) define mode 0.

So this should be ARM setting issue.

Thank you very much.