- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I would like to use the 25Fl064l NOR flash in QPI mode in order to execute code from the external memory. The flash is connected to an STM32F7xx microcontroller, which reads the data using memory mapped mode. After the setup phase the read access to the NOR flash is controlled by the memory controller of the MCU. The STM32F7xx QSPI peripheral has a 32 byte FIFO, which is used to prefetch data from the external data flash. The prefetch starts at every memory access and stops when the 32 byte FIFO is full.

I use a minimal example to test the code execution from the external memory: A very simple function is placed in the external NOR flash and called from the main loop running on the internal flash of the MCU. The code size of this simple function is 8 byte: 0x02, 0x46, 0x50, 0x18, 0x70, 0x47, 0x00, 0x00. The MCU is configured such that the instruction is only sent once at the first read operation (Quad I/O Read (QIOR 0xEB)). The mode byte of the read command is set to 0xA0, which causes the NOR flash to stay in high performance read mode.

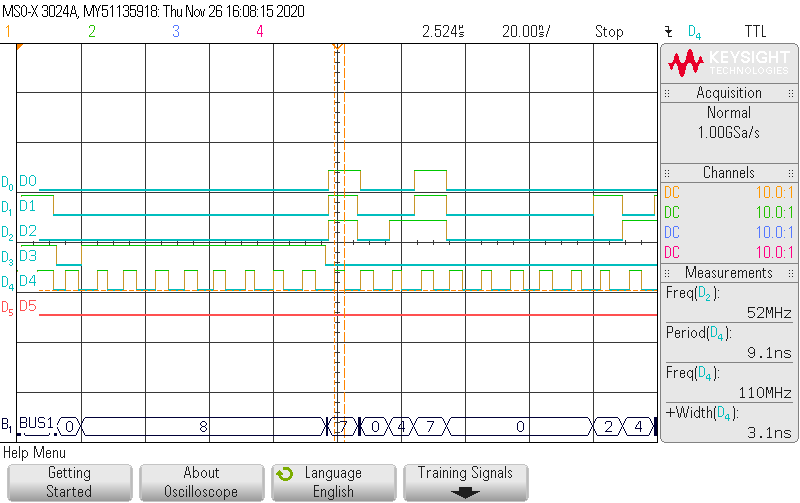

The following scope screen capture shows a memory access during code execution. It is a subsequent access, the read command instruction 0xEB was sent with the first command. (D0 - D1 -> SPI data lines, D4 -> SPI clock, D5 -> chip select)

The scope screen capture shows that the instructions are correctly read from the external flash: 0x02, 0x46 ...

If this simple function is called at the highest possible speed (from within a while loop), reading the instruction data sometimes fails. The corrupt data then causes a hard fault on the MCU. I captured two erroneous read sequences:

In the first sequence the NOR flash returns 0xFF for D0 - D3, followed by the correct data:

The returned data is:

0xFF, 0xFF, 0xFF, 0xFF, 0x70, 0x47, 0x00, 0x00

instead of

0x02, 0x46, 0x50, 0x18, 0x70, 0x47, 0x00, 0x00

The second sequence looks somehow folded:

The returned data is:

0xFF, 0xFF, 0xFF, 0xFF, 0x70, 0x47, 0x00, 0x00

instead of

0x70, 0x47, 0x00, 0x00, 0x02, 0x46, 0x50, 0x18

The following scope screen capture shows three subsequent read accesses when the function is called three times:

Two observations here:

- The data prefetch mechanism 'extends' the read access.

- The chip select signal goes inactive for a very short period of time

Does anyone have a hint what causes the read error?

Regards,

Daniel

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The maximum SPI clock frequency supported by Quad IO Read (EBh) command is 108MHz. But, in the images that you attached the frequency of clock signal is more than 108MHz (110MHz, 112MHz). Could you please double check the SPI clock frequency and test again?

Also, please make sure that the tCS (CS# High Time (Any Read Instructions), 20ns) spec is followed during multiple read operations.

As per my understanding, you are using 3 byte addressing mode. 6 clock cycles are required to send 3 bytes address in Quad mode. But, there are only 5 clock cycles before the mode bits (A0) in the first image that you attached. Could you please clarify this?

Thanks and Regards,

Sudheesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The maximum SPI clock frequency supported by Quad IO Read (EBh) command is 108MHz. But, in the images that you attached the frequency of clock signal is more than 108MHz (110MHz, 112MHz). Could you please double check the SPI clock frequency and test again?

Also, please make sure that the tCS (CS# High Time (Any Read Instructions), 20ns) spec is followed during multiple read operations.

As per my understanding, you are using 3 byte addressing mode. 6 clock cycles are required to send 3 bytes address in Quad mode. But, there are only 5 clock cycles before the mode bits (A0) in the first image that you attached. Could you please clarify this?

Thanks and Regards,

Sudheesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sudheesh

Many thanks for your prompt replay.

I modified the configuration of the QSPI peripheral on the microcontroller such that it meets the tCS (CS# High Time (Any Read Instructions), 20ns) specification. This solves the problem!

There are now 6 clock cycles during address transmission. There is a jitter on the SPI clock signal, but the frequency is correct.

Many thanks for your help!

Regards,

Daniel