Hyper RAM Forum Discussions

Is there any suggested footprint for the PG-BGA-24-803 package? Or any suggested pad size?

Thanks in advance!

Are there any Hyper RAM devices that can withstand 5+ krad?

If not, are there similar devices that would be recommended? I need:

- 256Mb+

- 200MHz+

- 1.8V

- Small package (currently use 6x8mm BGA and 2.18x2.76mm die

Thank you!

Show LessHi,

I have a board that has some nets incorrectly connected between the processor and the HyperRAM device(S27KS0642GABHV020). The processor is a NXP I.MXRT1052. The problem with the PCB is that the FlexSPI Data A and Data B signal groups are swapped.

I have reworked the board for fixing the connections but I think it will not be possible to operate the bus at full speed. I tried doing a test and there were read/write errors.

What's the minimum frequency the HyperRAM device can be operated with the IMXRT1062?

I know that hyperbus memories are very high speed devices, but since the IMXRT1062 is the one controlling the FlexSPI bus, that makes me think that it could be operated at lower frequencies. For instance, could I make it work at 30 MHz instead of 200 MHz? If this is possible I could configure the output buffer strength to low so to avoid signal integrity problems.

Thank you very much in advance,

Best regards,

Patricio

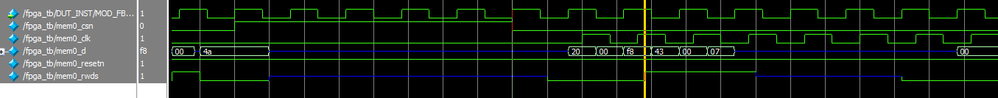

Show LessI have a question about the RWDS timing during the CA interval where simulation disagrees with the datasheet.

The simulation shows a HyperRAM write cycle where a refresh collision has occurred. RWDS changes in the middle of the CA interval signaling 2x latency. The datasheet only shows RWDS valid on CS# low.

If it is important to know when RWDS should be sampled to guarantee proper latency.

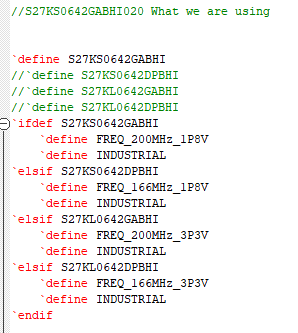

Infineon S27KS0642 1.8V 64Mb 200MHz

S27KS0642GABHI020

Clock is 125MHz. Initial latency set to 5. Variable latency enabled

Infineon memory model with the correct `define selected

Hi

we see memory test failures when running memtest in an eternal loop, it happens about once a day, and once it was running a week without failures. So I wonder if anyone has run a long memory test on some FPGA board? What board? What IP was used? How long was the longest test run?

So far I see several reports that there are failures on running memory tests, from different people, different FPGA boards, and different IP cores.

I am currently using OpenHBMC:

https://github.com/OVGN/OpenHBMC

With this board:

https://shop.trenz-electronic.de/de/CR00107-01-CRUVI-carrier-board-with-AMD-Spartan-7

I do not think there is a signal integrity issue: all HyperBUS wires are between 2 and 4 mm in length.

Thanks!

Show LessThere is an error in the DCARS footprint in the S70KS1282GABHB03 datasheet.

https://www.infineon.com/cms/en/search.html#!term=S70KS1282GABHB03&view=all

Section 12.2, Figure 37. The *DCARS*-capable part should have signals PSC and PSC# on pins B5 and C5, respectively. Those signals are not shown.

Can you please confirm that the footprint is wrong so that we can proceed forward with our board fabrication?

In the past we have used the 64Mbit DCARS-capable part which has the correct DCARS footprint pinout shown with the PSC/PSC# signals. We just want to make certain that the footprint is in error and that the PSC/PSC# pins are where we think they are.

Show LessWhy are there no HyperRAM parts with the DCARS feature in higher densities like 512Mbit?

The highest density hyperram with DCARS feature that I can find is 128Mbit.

The hyperram parts with the DCARS feature are a superior product in my opinion. Will higher density HyperRAMs w/ DCARS be released soon?

Show LessHello I'm looking for a verilog simulation model for the S70KL1281 (Hyper Ram).

Could you please point me the link to download it? (Prefer the model can be supported by xcelium and questasim)

** Note ** : I have been using the one provided in public (s27kl0642), but there is something more specific I would like to confirm with the exact variant in S70KL1281. Hope Infineon support team can help me with this.

Thanks a lot!

Regards,

SY

When I set up HyperBUS, it writes an indeterminate value (this is usually the case in the first generation as well).

When I write after this, I cannot write correctly.

I can't write directly in the debugger.

If I do a 16-byte write, for example, it appears that I can write from the middle.

When 16 characters are written as shown below, it seems to be able to write properly from the 5th character.

W: "HE2CT-1200A-3Z", R: "T-1200A-3Z

R: "T-1200A-3Z "

For example.

16 characters "HE2CT-1200A-3Z " should be

0x4000'0000~ and write

0x4000'0000~ is read in

If the character that should be in 0x4000'0004~ is written as

T-1200A-3Z" can be read.

This is the phenomenon.

If we follow the attached PCN and migration guidance document from Infineon, we need to set the latency to 7 clocks, but

RZ/A2M's latency clock setting seems to be only 5 or 6 clocks.

In the migration of HyperRAM GEN2.0 to the current RZ/A2M MPU (R7S921053VCBG), the clock cycle difference seems to have a particular impact.

The clock cycle difference seems to have a particular impact.

Is it possible to apply RZ/A2M vs HyperRAM Gen.2 itself?

Translated with DeepL

I am working on a HyperRAM controller in a MACHXO3 FPGA for this device.....

S27KS0642GABHI020

How is everyone handling the read cycle clock alignment? Variation over PVT is significant.

From the data sheet RWDS and DQout track each other tightly but they vary relative to the clock by a lot

1ns < tCKD < 5ns (clock to DQ valid)

0ns < tCKDI < 4.2ns (clock to DQ invalid)

My target clock is 125MHz (8ms)

At 125MHz the data valid window is....

3.0ns < tDV < 3.2ns

but the window center varies a LOT.

2.5ns < tCENTER < 6.6ns (delay from the clock edge)

For this to track over PVT is to use RWDS (edge aligned with the data) as the clock but RWDS is not free-running for a dynamic phase-lock.

A fixed delay from RWDS is possible but a known fixed clock period is required if guaranteed center alignment is desired.

What are your recommendations?

Show Less