Gate Driver ICs Forum Discussions

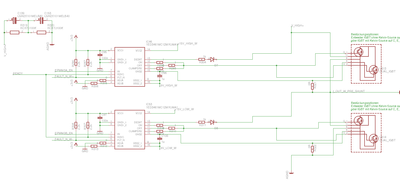

Hello, I am designing a BLDC, hall sensor, 3-phase motor driver circuit. The switching frequency is 15 kHz. Aluminum capacitor is thrown in the DC bus line. The necessary components for Bootstrap have been thrown. I control the duty with a potentiometer. While the engine is in the air, the engine spins up to high speeds. However, there is a problem under load, there is always a short circuit between the VCC-LO pins of a gate driver. I am using STM32F303RE as control IC and I wrote the software. In some cases, the potentiometer becomes dysfunctional, does not detect it, I have to reset it.

Why are VCC-LO pins always burning in this integrated?

Show LessHi

Can I use 2ED2304S06F to drive IHW20N65R5 IGBTs?

Can I use the 2ED2304S06F driver with an STM32G0 series microcontroller?

Note: STM32G0 works with 3.3v.

Thanks.

Show LessNow,I want to use IR2104 to control the full-bridge inverter circuit to realize the conversion of DC to AC. The normal way of use is that two ICs control four MOSFETs to drive a full-bridge circuit, but I need more at the same time.

Can I use two ICs to drive more than one full-bridge inverter circuit? That is, two ICs are used to control more than four MOSFETs, such as a dozen or tow dozen.

Show LessDear Team,

Good morning.

We are using your 1EDI60N12AF in our simulation.

I would like to confirm few things below before explaining the issue.

We have used/given,

1.VCC1=5V supply(DC)

2.INP=3.3V ADC having 10KHz switching frequency and 60% duty cycle

3.INN-Grounded

4.VCC2=15V Supply(DC)

5.Gnd2=- 5V(Negative 5V) DC supply given in order to completely turn of switch(IGBT/mosfet)

Issue in simulation:

The given model is only working for VCC1=3.3V

If we give 5V in VCC1 then in output we don't get gate pulse instead we get -5V DC(steady DC Value).

As per datasheet we can give up to 15V to VCC1 pin.

Kindly provide us support and solution as early as possible.

Thank you,

Girish Kantharaju

while opening through macro wizard is showing error in 315th line. the error was missing command

.SUBCKT 1ED3322MC12N VCC1 INP INN RDY NFLT NRST GND1 VCC2 DESAT CLAMP OUTH OUTL GND2 VEE2

X_DRIVER VCC1 INP INN GND1 VCC2 OUTH OUTL CLAMP VEE2 RDY NFLT NRST DESAT GND2 ONE_ED3322MC12N_GD_CT_TEMPLATE

D_GND1_INP GND1 INP ONE_ED3322MC12N_DZ_ESD_18

D_GND1_INN GND1 INN ONE_ED3322MC12N_DZ_ESD_18

D_GND1_VCC1 GND1 VCC1 ONE_ED3322MC12N_DZ_ESD_18

.MODEL ONE_ED3322MC12N_DZ_ESD_18 D( IS=1.0E-9 N=1.0 RS=10 BV=18 IBV=5.0E-3 XTI=0)

D_GND2_VCC2 VEE2 VCC2 ONE_ED3322MC12N_DZ_ESD_40

.MODEL ONE_ED3322MC12N_DZ_ESD_40 D( IS=1.0E-9 N=1.0 RS=10 BV=40 IBV=5.0E-3 XTI=0)

RGND VEE2 GND1 10MEG

CGND VEE2 GND1 5P

C_VCC1 VCC1 GND1 10F

C_INP INP GND1 10F

C_INN INN GND1 10F

C_RDY RDY GND1 10F

C_NFLT NFLT GND1 10F

C_NRST NRST GND1 10F

C_VCC2 VCC2 VEE2 10F

C_DESAT DESAT GND2 10F

C_CLAMP CLAMP VEE2 10F

R_CLAMP CLAMP VEE2 10MEG

C_OUTH OUTH VEE2 10F

C_OUTL OUTL VEE2 10F

.ENDS

.SUBCKT ONE_ED3322MC12N_GD_CT_TEMPLATE VCC1 INP INN GND1 VCC2 OUTH OUTL CLAMP VEE2 RDY NFLT NRST DESAT GND2 PARAMS: P_C_PW_MIN=

+ 1.1683E-08 P_INH_TH=3.3 P_INL_TH=1.7 P_R_INP=50E03 P_R_INN=50E03 P_VCC1_UVH=2.9 P_VCC1_UVL=2.7 P_VCC2_UVH=13.6 P_VCC2_UVL=12.6

+ P_C_UVL_START=1E-15 P_C_UVL_RDYC=1E-15 P_R_RDY_UP=50E+03 P_I_RDY_DSCH=15E-03 P_R_NFLT_UP=50E+03 P_I_NFLT_DSCH=15E-03 P_R_NRST_UP=

+ 50E+03 P_NRSTH_TH=4 P_NRSTL_TH=1 P_C_RST_MIN=1.1683E-08 P_C_TRST=3.3381E-07 P_C_TPD40N=5.64583E-09 P_C_TPDON=4.7982E-09 P_C_TDPOFF=

+ 1.560505E-09 P_R_RISE=4 P_C_RISE=18E-09 P_R_FALL=5 P_C_FALL=13E-09 P_WH=1M P_LH=1U P_LAMBDAH=0.121 P_KPH=0.000251 P_VTOH=-1 P_RBH=1

+ P_VGSH=6.4 P_RGH=1 P_CGSOH=100E-12 P_WL=1M P_LL=1U P_LAMBDAL=0.071 P_KPL=0.000311 P_VTOL=1 P_RBL=1 P_VGSL=7.9 P_RGL=1 P_CGSOL=

+ 100E-12 P_VDESAT=9 P_IDESATC=510E-06 P_IDESATDSCH=150E-03 P_C_TLEB_D=1.3353E-07 P_C_TDESATFIL=8.3453E-08 P_C_TDESATOUT=3.2496E-08

+ P_C_TDESATFLT=3.3381E-07 P_TH_CLAMP=2.1 P_VGSN_CL=3.3 P_NLAMBDA_CL=0.101 P_NKP_CL=0.000916 P_IS=1E-15 P_N=1.3 P_RS=0.3 P_IS_CL=

+ 1E-15 P_N_CL=1.3 P_RS_CL=0.3 P_IQ1=0.001 P_IQ2=0.002 P_IS_DES=1E-15 P_N_DES=1.3 P_RS_DES=0.3

X_IN_STAGE VCC1 INP INN INPD INND GND1 ONE_ED3322MC12N_INPUT_BLK PARAMS: P_INH_TH={P_INH_TH} P_INL_TH={P_INL_TH} P_C_PW_MIN=

+ {P_C_PW_MIN} P_R_INP={P_R_INP} P_R_INN={P_R_INN}

X_UVL_VCC1 VCC1 UVL1_DEL GND1 ONE_ED3322MC12N_UVL_VCC PARAMS: P_VCC_UVH={P_VCC1_UVH} P_VCC_UVL={P_VCC1_UVL} P_C_UVL_START=

+ {P_C_UVL_START} P_C_UVL_RDYC={P_C_UVL_RDYC}

X_UVL_VCC2 VCC2 UVL2_DEL GND2 ONE_ED3322MC12N_UVL_VCC PARAMS: P_VCC_UVH={P_VCC2_UVH} P_VCC_UVL={P_VCC2_UVL} P_C_UVL_START=

+ {P_C_UVL_START} P_C_UVL_RDYC={P_C_UVL_RDYC}

X_RDY VCC1 RDY UVL1_DEL UVL2_DEL GND1 ONE_ED3322MC12N_RDY_BLK PARAMS: P_R_RDY_UP={P_R_RDY_UP} P_I_RDY_DSCH={P_I_RDY_DSCH}

X_FLTN VCC1 NFLT FLT2 EN_FLT NRST_CLR GND1 ONE_ED3322MC12N_FLTN_BLK PARAMS: P_R_NFLT_UP={P_R_NFLT_UP} P_I_NFLT_DSCH={P_I_NFLT_DSCH}

X_RST VCC1 NRST NRST_MIN NRST_CLR GND1 ONE_ED3322MC12N_RST_BLK PARAMS: P_R_NRST_UP={P_R_NRST_UP} P_NRSTH_TH={P_NRSTH_TH} P_NRSTL_TH=

+ {P_NRSTL_TH} P_C_RST_MIN={P_C_RST_MIN} P_C_TRST={P_C_TRST}

E_PWM PWM 0 VALUE { IF( V(UVL1_DEL)<0.5 & V(UVL2_DEL,0)<0.5 & V(INPD)>0.5 & V(INND)<0.5 & V(EN_FLT)<0.5 & V(NRST_MIN)>0.5, 1,0 ) }

X_OUT_STAGE PWM GATEN GATEP EN_DESAT OUTH OUTL DESATOUT OFF_DD CLAMP VCC2 VEE2 ONE_ED3322MC12N_OUT_STAGE PARAMS: P_WH={P_WH} P_LH=

+ {P_LH} P_LAMBDAH={P_LAMBDAH} P_KPH={P_KPH} P_VTOH={P_VTOH} P_RBH={P_RBH} P_VGSH={P_VGSH} P_RGH={P_RGH} P_CGSOH={P_CGSOH} P_WL=

+ {P_WL} P_LL={P_LL} P_LAMBDAL={P_LAMBDAL} P_KPL={P_KPL} P_VTOL={P_VTOL} P_RBL={P_RBL} P_VGSL={P_VGSL} P_RGL={P_RGL} P_CGSOL=

+ {P_CGSOL} P_C_TPD40N={P_C_TPD40N} P_C_TPDON={P_C_TPDON} P_C_TDPOFF={P_C_TDPOFF} P_R_RISE={P_R_RISE} P_C_RISE={P_C_RISE} P_R_FALL=

+ {P_R_FALL} P_C_FALL={P_C_FALL} IS_CL={P_IS} N_CL={P_N} RS_CL={P_RS}

X_DESAT VCC2 DESAT INPD OFF_DD GATEP OUTH DESATOUT FLT2 GND2 VEE2 ONE_ED3322MC12N_DESAT_BLK PARAMS: VDESAT={P_VDESAT} IDESATC=

+ {P_IDESATC} IDESATDSCH={P_IDESATDSCH} P_TLEB_D={P_C_TLEB_D} P_TDESATFIL={P_C_TDESATFIL} P_TDESATOUT={P_C_TDESATOUT} P_TDESATFLT=

+ {P_C_TDESATFLT} IS_CL={P_IS_DES} N_CL={P_N_DES} RS_CL={P_RS_DES}

X_CLAMP PWM GATEN OUTH VCC2 VEE2 CLAMP ONE_ED3322MC12N_MILLER_CLAMP PARAMS: P_TH_CLAMP={P_TH_CLAMP} P_VGSN_CL={P_VGSN_CL} P_NLAMBDA_CL=

+ {P_NLAMBDA_CL} P_NKP_CL={P_NKP_CL} IS_CL={P_IS_CL} N_CL={P_N_CL} RS_CL={P_RS_CL}

X_CC_EMULATOR VCC1 VCC2 GND1 GND2 ONE_ED3322MC12N_QUIESCENT_CRT PARAMS: P_IQ1={P_IQ1} P_IQ2={P_IQ2}

.ENDS ONE_ED3322MC12N_GD_CT_TEMPLATE

.SUBCKT ONE_ED3322MC12N_INPUT_BLK VCC INP INN INPD INND GND PARAMS: P_INH_TH=4.0 P_INL_TH=1.0 P_C_PW_MIN=3.0E-9 P_R_INP=1K P_R_INN=1K

R_INP_DW INP GND {P_R_INP}

R_INN_UP VCC INN {P_R_INN}

E_TH_UP TH_UP 0 VALUE { V(VCC,GND)*0.65}

E_TH_DW TH_DW 0 VALUE { V(VCC,GND)*0.35}

X_INP INP D_INP TH_UP TH_DW GND ONE_ED3322MC12N_STP_IDEAL_TH

X_INN INN D_INN TH_UP TH_DW GND ONE_ED3322MC12N_STP_IDEAL_TH

X_INPMIN D_INP INPD ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_C_PW_MIN} P_TH_UP=0.95 P_TH_DW=0.05

X_INNMIN D_INN INND ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_C_PW_MIN} P_TH_UP=0.95 P_TH_DW=0.06

.ENDS

.SUBCKT ONE_ED3322MC12N_RDY_BLK VCC RDY UVL1_DEL UVL2_DEL GND1 PARAMS: P_R_RDY_UP=1E+3 P_I_RDY_DSCH=5E-03

R_RDYC_UP VCC RDY {P_R_RDY_UP}

E_EN_RDY EN_RDY 0 VALUE { IF ( V(UVL1_DEL)>0.5 | V(UVL2_DEL)>0.5, 1,0 ) }

R_EN_RDY EN_RDY EN_RDYD 1E+03

C_EN_RDY EN_RDYD 0 1E-12

G_RDY_DSCH RDY GND1 VALUE { TABLE(V(RDY,GND1), 0,0, 0.1,0, 0.2,1 )*V(EN_RDYD)*{P_I_RDY_DSCH} }

R_RDY_DSCH RDY GND1 1E12

.ENDS

.SUBCKT ONE_ED3322MC12N_FLTN_BLK VCC1 NFLT FLT2 EN_FLT NRST_CLR GND1 PARAMS: P_R_NFLT_UP=1E+06 P_I_NFLT_DSCH=5E-03

R_NFLT_UP VCC1 NFLT {P_R_NFLT_UP}

X_INV FLT2 FLT2_INV ONE_ED3322MC12N_INV_GATE

X_FF FLT2_INV NRST_CLR EN_FLT NQEN ONE_ED3322MC12N_SR_FF

G_FLT_DSCH NFLT GND1 VALUE { TABLE( V(NFLT,GND1), 0,0, 0.1,0, 0.2,1 )*V(EN_FLT)*{P_I_NFLT_DSCH} }

R_FLT_DSCH NFLT GND1 1E12

.ENDS

.SUBCKT ONE_ED3322MC12N_RST_BLK VCC1 NRST NRST_MIN NRST_CLR GND1 PARAMS: P_R_NRST_UP=1E+06 P_NRSTH_TH=4 P_NRSTL_TH=1 P_C_RST_MIN=

+ 3.0E-9 P_C_TRST=3.0E-9

R_NRST_UP VCC1 NRST {P_R_NRST_UP}

E_TH_UP_NRST TH_UP_NRST 0 VALUE { V(VCC1,GND1)*0.65}

E_TH_DW_NRST TH_DW_NRST 0 VALUE { V(VCC1,GND1)*0.35}

X_INP NRST NRST_TH TH_UP_NRST TH_DW_NRST GND1 ONE_ED3322MC12N_STP_IDEAL_TH

X_INMIN NRST_TH NRST_MIN ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_C_RST_MIN} P_TH_UP=0.95 P_TH_DW=0.051

X_INMIN1 NRST_TH CLR ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_C_TRST} P_TH_UP=0.95 P_TH_DW=0.051

E_NRST_CLR NRST_CLR 0 VALUE { IF( V(NRST_TH)<0.5 & V(CLR)<0.5, 1,0) }

.ENDS

.SUBCKT ONE_ED3322MC12N_OUT_STAGE PWM GATEN GATEP EN_DESAT OUTH OUTL DESATOUT EN_OFF CLAMP VCC2 GND2 PARAMS: P_WH=1M P_LH=1U P_LAMBDAH=

+ 0.12 P_KPH=10U P_VTOH=-1 P_RBH=1 P_VGSH=10.3 P_RGH=1 P_CGSOH=100P P_WL=1M P_LL=1U P_LAMBDAL=0.07 P_KPL=30U P_VTOL=1 P_RBL=1 P_VGSL=

+ 6.7 P_RGL=1 P_CGSOL=100P P_C_TPD40N=5.64583E-09 P_C_TPDON=4.9982E-09 P_C_TDPOFF=2.5505E-09 P_R_RISE=4 P_C_RISE=10N P_R_FALL=5

+ P_C_FALL=15N IS_CL=1E-15 N_CL=0.8624838364971924 RS_CL=0.3

X_TDPON2_30N PWM TPDON_30N ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY=10.6E-09 P_TH_UP=0.9 P_TH_DW=0.1

E_ENON TPDON 0 VALUE { IF( V(TPDON_30N)>0.5, 1,0) }

R_ON_DD TPDON EN_ON {P_R_RISE}

C_ON_DD EN_ON 0 {P_C_RISE}

X_TDPOFF_20N PWM TPDOFF_20N_1 ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY=2.50505E-09 P_TH_UP=0.999 P_TH_DW=0.001

X_TDPOFF1_20N TPDOFF_20N_1 TPDOFF_20N ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY=2.70505E-09 P_TH_UP=0.999 P_TH_DW=0.001

E_ENOFF TDPOFF 0 VALUE { IF( V(TPDOFF_20N)>0.5 & V(DESATOUT)<0.5, 1,0 ) }

R_OFF_DD TDPOFF EN_OFF {P_R_FALL}

C_OFF_DD EN_OFF 0 {P_C_FALL}

E_GATEP VCC2 GATEP VALUE { V(TPDON_30N,0)*{P_VGSH}*V(EN_ON)*(1-V(DESATOUT)) }

E_GATEN GATEN GND2 VALUE { (1-V(TDPOFF,0))*{P_VGSL}*(1-V(EN_OFF)) }

M_UP OUTH GATEP VCC2 VCC2 ONE_ED3322MC12N_LO_PMOS

.MODEL ONE_ED3322MC12N_LO_PMOS PMOS ( LEVEL=1 W={P_WH} L={P_LH} CGSO={P_CGSOH} LAMBDA={P_LAMBDAH} KP={P_KPH} VTO={P_VTOH} RB={P_RBH}

+ RG={P_RGH})

M_DW OUTL GATEN GND2 GND2 ONE_ED3322MC12N_LO_NMOS

.MODEL ONE_ED3322MC12N_LO_NMOS NMOS ( LEVEL=1 W={P_WL} L={P_LL} CGSO={P_CGSOL} LAMBDA={P_LAMBDAL} KP={P_KPL} VTO={P_VTOL} RB={P_RBL}

+ RG={P_RGL})

D_CLAMP OUTH VCC2 ONE_ED3322MC12N_DCLAMP

D_CLAMP1 OUTL VCC2 ONE_ED3322MC12N_DCLAMP

.MODEL ONE_ED3322MC12N_DCLAMP D ( IS={IS_CL} N={N_CL} RS={RS_CL} )

.ENDS

.SUBCKT ONE_ED3322MC12N_DESAT_BLK VCC2 DESAT INPD OFF_DD GATEP OUT DESATOUT FLT2 GND2 VEE2 PARAMS: VDESAT=9 IDESATC=500E-06 IDESATDSCH=

+ 14E-03 P_TLEB_D=1.3353E-07 P_TDESATFIL=8.3453E-08 P_TDESATOUT=1.1684E-07 P_TDESATFLT=6.6762E-07 IS_CL=1E-15 N_CL=0.8624838364971924

+ RS_CL=0.3

E_EN_CH EN_CH 0 VALUE { IF( V(VCC2,GATEP)>0.8 & V(OUT,VEE2)>3, 1,0 ) }

X_TLEB_D EN_CH EN_CH_LEB ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_TLEB_D} P_TH_UP=0.95 P_TH_DW=0.05

G_DESAT_CH VCC2 DESATI VALUE { TABLE( V(VCC2,DESAT),0,0,0.1,1)*V(EN_CH_LEB)*{IDESATC} }

R_UP2 VCC2 DESATI 1E+12

V_DESAT DESATI DESAT 0

G_GND2 GND2 VCC2 VALUE { I(V_DESAT) }

E_COMP COMP_DESAT 0 VALUE {IF( V(DESAT,GND2) >= {VDESAT} & V(OUT,VEE2)>10 & V(EN_CH_LEB)>0.5, 1.0,0.0 )}

E_DESAT_1 RST1 0 VALUE { IF( V(INPD)<0.5 & V(DESAT)<0.5, 1,0 ) }

X_TDESATFIL1 COMP_DESAT DESATFIL ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_TDESATFIL} P_TH_UP=0.95 P_TH_DW=0.05

XLATCH DESATOUT1 RST1 DESATOUT QN ONE_ED3322MC12N_SRLATCH

X_LATCH_COMP EN_CH_LEB RST1 QTEST NQTEST ONE_ED3322MC12N_SRLATCH

E_TEST TEST 0 VALUE {V(QTEST)}

E_TEST1 TEST1 0 VALUE {(1-V(TEST))}

X_TDESATOUT DESATFIL DESATOUT1 ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_TDESATOUT} P_TH_UP=0.95 P_TH_DW=0.05

X_TDESATFLT1 DESATFIL FLT21 ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY=6.3453E-08 P_TH_UP=0.95 P_TH_DW=0.05

X_TDESATFLT2 FLT21 FLT22 ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY=6.3453E-08 P_TH_UP=0.95 P_TH_DW=0.05

X_TDESATFLT3 FLT22 FLT23 ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY=6.3453E-08 P_TH_UP=0.95 P_TH_DW=0.05

X_TDESATFLT FLT23 FLT2 ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY=5.7453E-08 P_TH_UP=0.95 P_TH_DW=0.05

E_DIS DIS 0 VALUE { IF(V(DESATFIL) > 0.5 | V(DESATOUT) > 0.5 , 1 ,0 )}

G_DESAT_DSCH DESAT GND2 VALUE { TABLE( V(DESAT,GND2), 0,0, 0.1,0.15, 0.5, 0.5, 0.6,1 )*V(DESATOUT)*{IDESATDSCH} }

R_DESAT_DSCH DESAT GND2 100E12

E_GATEN_DESAT GATEN_DESAT GND2 VALUE { (V(TEST1,0))*2.1 }

M_DW_DESAT DESAT GATEN_DESAT GND2 GND2 ONE_ED3322MC12N_LO_NMOS

.MODEL ONE_ED3322MC12N_LO_NMOS NMOS ( LEVEL=1 W=1M L=1U CGSO=100E-12 LAMBDA=0.001 KP=0.00017 VTO=1 RB=1 RG=1 )

D_CLAMP DESAT VCC2 ONE_ED3322MC12N_DCLAMP

.MODEL ONE_ED3322MC12N_DCLAMP D ( IS={IS_CL} N={N_CL} RS={RS_CL} )

.ENDS

.SUBCKT ONE_ED3322MC12N_MILLER_CLAMP PWM GATEN OUT VCC2 GND2 CLAMP PARAMS: P_TH_CLAMP=2.0 P_VGSN_CL=4.95 P_NLAMBDA_CL=0.13 P_NKP_CL=

+ 267E-06 IS_CL=1E-15 N_CL=0.8 RS_CL=0.3

E_TH_CL VTH_CL 0 VALUE { IF( ( V(CLAMP,GND2)<={P_TH_CLAMP} & V(PWM)<0.5 ), 1,0 ) }

X_GATEN VTH_CL VTH_CL_DEL ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY=15E-9 P_TH_UP=0.95 P_TH_DW=0.95

E_GATEN GATEN_CL GND2 VALUE { {P_VGSN_CL}*V(VTH_CL_DEL) }

M_N_CLAMP CLAMP GATEN_CL GND2 GND2 ONE_ED3322MC12N_CL_NMOS

R_CLAMPCNV CLAMP GND2 1E9

.MODEL ONE_ED3322MC12N_CL_NMOS NMOS ( LEVEL=1 W=1M L=1U CGSO=100P LAMBDA={P_NLAMBDA_CL} KP={P_NKP_CL} VTO=1 RB=10 RG=1)

.MODEL ONE_ED3322MC12N_DCLAMP D ( IS={IS_CL} N={N_CL} RS={RS_CL} )

G_CLAMP CLAMP VCC2 VALUE={ TABLE(V(CLAMP,VCC2), 0,0 , 0.3,20M , 0.9,100M , 1.7,500M) }

.ENDS

.SUBCKT ONE_ED3322MC12N_QUIESCENT_CRT VCC1 VCC2 GND1 GND2 PARAMS: P_IQ1=1M P_IQ2=1M

G_VCC1 VCC1 GND1 VALUE { TABLE( V(VCC1,GND1), 0,0, 0.1,1U, 1,100U, 0.8*5,{P_IQ1} ) }

R_VCC1 VCC1 GND1 1E+12

G_QCC VCC2 GND2 VALUE { TABLE( V(VCC2,GND2), 0,0, 0.1,1U, 1,100U, 0.8*10,{P_IQ2} ) }

R_QCC VCC2 GND2 1E+12

.ENDS

.SUBCKT ONE_ED3322MC12N_UVL_VCC VCC UVL_OUT GND PARAMS: P_VCC_UVH=1 P_VCC_UVL=1 P_C_UVL_START=1E-15 P_TH_STARTDW=0.999 P_TH_STARTUP=

+ 0.001 P_C_UVL_RDYC=1E-15 P_TH_UVLRDYCDW=0.999 P_TH_UVLRDYCUP=0.001

X_UVL VCC UVL_DET GND ONE_ED3322MC12N_STN_IDEAL PARAMS: P_TH_UP={P_VCC_UVH} P_TH_DW={P_VCC_UVL}

X_UVL_START UVL_DET UVL_START ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_C_UVL_START} P_TH_UP={P_TH_STARTDW} P_TH_DW={P_TH_STARTUP}

X_UVL_UVL1LRDYC UVL_DET UVL_UVL1LRDYC ONE_ED3322MC12N_ADV_FILT PARAMS: P_C_DELAY={P_C_UVL_RDYC} P_TH_UP={P_TH_UVLRDYCDW} P_TH_DW=

+ {P_TH_UVLRDYCUP}

X_OR UVL_START UVL_UVL1LRDYC UVL_DEL ONE_ED3322MC12N_OR_GATE

E_UVL_OUT UVL_OUT 0 VALUE { V(UVL_DEL) }

.ENDS

.SUBCKT ONE_ED3322MC12N_STP_IDEAL IN OUT GND PARAMS: P_TH_UP=0.9 P_TH_DW=0.1

E_UP UP 0 VALUE { IF( V(IN,GND)>={P_TH_UP} | V(DW)<0.5, 1,0 ) }

E_DW DW 0 VALUE { IF( V(IN,GND)<={P_TH_DW} | V(UP)<0.5, 1,0 ) }

E_OUT OUT 0 VALUE { V(UP) }

.ENDS

.SUBCKT ONE_ED3322MC12N_STP_IDEAL_TH IN OUT TH_UP TH_DW GND

E_UP UP 0 VALUE { IF( V(IN,GND)>=V(TH_UP) | V(DW)<0.5, 1,0 ) }

E_DW DW 0 VALUE { IF( V(IN,GND)<=V(TH_DW) | V(UP)<0.5, 1,0 ) }

E_OUT OUT 0 VALUE { V(UP) }

.ENDS

.SUBCKT ONE_ED3322MC12N_STN_IDEAL IN OUT GND PARAMS: P_TH_UP=0.9 P_TH_DW=0.1

E_UP UP 0 VALUE { IF( V(IN,GND)>={P_TH_UP} | V(DW)<0.5, 1,0 ) }

E_DW DW 0 VALUE { IF( V(IN,GND)<={P_TH_DW} | V(UP)<0.5, 1,0 ) }

E_OUT OUT 0 VALUE { V(DW) }

.ENDS

.SUBCKT ONE_ED3322MC12N_ADV_FILT IN OUT PARAMS: P_R_DELAY=1 P_C_DELAY=10E-9 P_TH_UP=0.999 P_TH_DW=0.001

R_RISE IN IN_DEL {P_R_DELAY}

C_RISE IN_DEL 0 {P_C_DELAY}

X_CMP IN_DEL OUT 0 ONE_ED3322MC12N_STP_IDEAL PARAMS: P_TH_UP={P_TH_UP} P_TH_DW={P_TH_DW}

.ENDS

.SUBCKT ONE_ED3322MC12N_INV_GATE IN OUT

E_OUT OUT 0 VALUE { IF( V(IN,0)>0.5, 0,1 ) }

.ENDS

.SUBCKT ONE_ED3322MC12N_NAND_GATE IN1 IN2 OUT

E_OUT OUT_INT 0 VALUE { IF( (V(IN1,0)>0.5 & V(IN2,0)>0.5), 0,1 ) }

R_OUT OUT_INT OUT 10

C_OUT OUT 0 10E-12

.ENDS

.SUBCKT ONE_ED3322MC12N_OR_GATE IN1 IN2 OUT

E_OUT OUT_INT 0 VALUE { IF( (V(IN1,0)>0.5 | V(IN2,0)>0.5), 1,0 ) }

R_OUT OUT_INT OUT 10

C_OUT OUT 0 1E-12

.ENDS

.SUBCKT ONE_ED3322MC12N_SR_FF SET RESET OUT NOUT

X_INV OUT_RESET OUT_RESET_INV ONE_ED3322MC12N_INV_GATE

X_SR OUT_SET OUT_RESET Q QN ONE_ED3322MC12N_SRLATCH

X_FF1 QN OUT_RESET_INV SET OUT_SET ONE_ED3322MC12N_FF_IDEAL

X_AND QN SET RST_FF2 ONE_ED3322MC12N_NAND_GATE

X_FF2 Q RST_FF2 RESET OUT_RESET ONE_ED3322MC12N_FF_IDEAL

E_OUT OUT 0 VALUE { V(Q) }

E_NOUT NOUT 0 VALUE { V(QN) }

.ENDS

.SUBCKT ONE_ED3322MC12N_FF_IDEAL DIN RSTN CLK Q

V_RSTN RSTND 0 PWL (0,1) (1E-9,1) (2E-9,0)

E_RST RST 0 VALUE {V(RSTN)-V(RSTND)}

X_NAND1 DIN OUT5 OUT1 ONE_ED3322MC12N_NAND_GATE

X_NAND2 RST CLK OUT2 ONE_ED3322MC12N_NAND_GATE

X_NAND3 OUT1 OUT6 OUT3 ONE_ED3322MC12N_NAND_GATE

X_NAND4 RST OUT3 OUT4 ONE_ED3322MC12N_NAND_GATE

X_NAND5 OUT4 OUT2 OUT5 ONE_ED3322MC12N_NAND_GATE

X_INV OUT4 OUT_INV ONE_ED3322MC12N_INV_GATE

X_NAND6 OUT2 OUT_INV OUT6 ONE_ED3322MC12N_NAND_GATE

X_NAND7 OUT5 Q QN ONE_ED3322MC12N_NAND_GATE

X_NAND8 QN OUT6 Q ONE_ED3322MC12N_NAND_GATE

.ENDS

.SUBCKT ONE_ED3322MC12N_SRLATCH SET RESET Q QN

E_QN QN1 0 VALUE {IF( (V(SET,0)<0.5 & V(Q,0)<0.5 )| TIME<1NS,1,0)}

R_QN QN1 QN 10

C_QN QN 0 0.1E-12

E_Q Q1 0 VALUE {IF( (V(QN,0)<0.5 & V(RESET,0)<0.5 ) ,1,0)}

R_Q Q1 Q 10

C_Q Q 0 0.1E-12

RQ Q 0 100E+6

.ENDS ONE_ED3322MC12N_SRLATCH

Hello,

Hello,

I am using an EiceDRIVER 1ED34x1Mc12M for controlling an IGBT but the driver's Ready Signal is always 0.

After applying voltage to the driver FAULT_N switches to 1 (which means no error) but RDYC is alway 0 (which means driver is not ready).

Here is the schematic of my application.

READY and the FAULT Pins of the driver are connected to inputs of my microcontroller. EPWM3a_EN and EPWM3b_EN are connected to the PWM outputs of my controller and configured as outputs.

For testing purpose I only applied 32V to V_HIGH+. As IGBTs I am currently using the RGT50TM65D from ROHM which is a normal IGBT without Kelvin Source.

I have tried different resistors for ADJA and ADJB but RYDC never changes to 1.

Is there something wrong with my schematic? Do you have any tips for me how I can debug this?

Best regards,

Johannes

Show Less

Please tell us one point about Gate Driver.

Is it possible to use a CT type 2ch output Gate Driver for the midpoint part of the H6.5 circuit used in the PCS?

If there are independent GND terminals on the H side and L side, I think there will be no problem with the operation itself, but does Infineon recommend using it in a 2ch product?

Or do you recommend using 1ch products?

■ 2ch product model number

・Model number: 2ED020I06-FI

・Model number: 2ED020I12-F2

Best regards,

Show LessHi, I am trying to establish the rise time of the 1ED3142 gate driver @ Vvcc-Vvee = 20V.

The data sheet states 20nS maximal rise time but no minimum or typical Value. I would like to achieve as short a rise time as the mosfet will allow , if possible.

Input capacitance of the Mosfet is 579pF, gate charge is 37nC, rise time is 8nS.

The function generator has a 7ns rise time output signal.

What will be the probably output rise time of the 1ED3142 gate driver?

Thank you

eccone

Show Less