Code Examples Forum Discussions

A new version of the component (v.1.0) is provided below

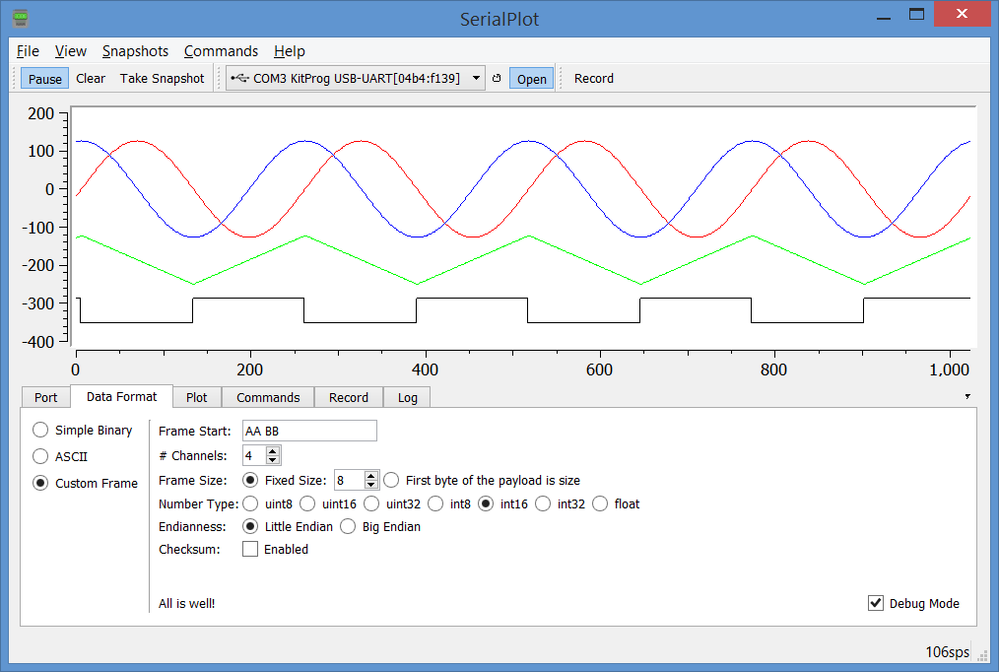

Provided below is custom component (SerialPlot v0.0) for interfacing with real-time plotting software SerialPlot.

Hackaday.io: SerialPlot - Realtime Plotting Software

The component implements interface to the real-time charting software SerialPlot. Using this component, PSoC data can be easily visualized on personal computer (Linux, Mac & Windows). Component doesn’t consume hardware resources, performing all operations by CPU, which is useful for systems with little resources, such as PSoC4. Multiple instances of the component can run simultaneously in the project.

Component features:

Data types: int8, int16, int32, uint8, uint16, uint32, float

Up to 8 channel output

The component was tested using CY8KIT-059 PSoC5 prototyping kit and CY8KIT-042 PSoC4 Pioneer Kit. Demo projects are provided.

Attached archive contains component library, component datasheet and demo projects for PSoC5 and PSoC4. Please read installation instructions in the readme.txt.

The component provided as-is, no liabilities. It is free to use and modify.

/odissey1

P.S. Demo projects use optional annotation components (which are also provided here in Support_libs.zip):

PSoC Annotation Library: PSoC Annotation Library v1.0

KIT-042 annotation stub: KIT-042: annotation component for CY8CKIT-042 Pioneer Kit

Download SerialPlot: Hackaday.io: SerialPlot - Realtime Plotting Software

Figure 1. SerialPlot demo project schematic.

Figure 2. Project data output to SerialPlot graphic software.

Description Overview

I wrote code to make a sound using the slider of the CY8CKIT-042 PSoC 4 Pioneer Kit.

1. Get a position on the slider.

2. Set the PWM value according to the location and output as sound.

3. If the position changes, change the value of PWM.

4. If the finger is separated, the PWM output stops.

Prerequisites

• Evaluation Board: CY8CKIT-042 PSoC 4 Pioneer Kit

• Piezoelectric buzzer

• IDE name: PSoC Creator 4.4

procedure

1.P3.5 and GND Connected the buzzer to the PIN.

2. Run the project attached to this topic and touch the slider on the evaluation board with your finger to make a sound.

If you want to change the connection of the buzzer, please change it from the Pin settings.

smartconx_target@Q!w2e3r4t5y6u7i8o9p0||/t5/%E3%82%B3%E3%83%BC%E3%83%89%E4%BE%8B/CY8CKIT-042%E3%82%92%E4%BD%BF%E7%94%A8%E3%81%97%E3%81%A6%E3%82%B9%E3%83%A9%E3%82%A4%E3%83%80%E3%83%BC%E3%81%AE%E4%BD%8D%E7%BD%AE%E3%81%AB%E3%82%88%E3%81%A3%E3%81%A6%E9%9F%B3%E3%82%92%E5%A4%89%E3%81%88%E3%82%8B/td-p/501704

Show LessDears,

please find my solution for the calculation of the parity value for 32-bit data words in 64K SRAM blocks with 32-bit access attached. The code is based on the algorithm described in the TRAVEO™ T2G Automotive Body Controller

Entry Family Architecture TRM, Document No. 002-19314 Rev. *H, section 10.3.4 ECC Parity Generation by Software.

The function uint8_t ECC32_RAM_parity(uint32_t ram_addr, uint32_t data) returns the correct parity value when called with the ram_address (has to be 32 bit alligned) and the data stored in this address.

Use this function also to calculate parity values for data with one or more bit errors.

There are examples in the SDL with correct parity values:

SDL 7.8.0, T2G_Sample_Driver_Library_7.8.0\tviibe1m\src\examples\sram\ecc\main_cm0plus.c.

Excerpt:

#define RAM_0_ADDRESS (0x08000800)

#define RAM_0_DATA (0x5A5A5A5A)

#define RAM_0_CORRECT_PARITY (0x6E)

#define RAM_0_ONEBIT_PARITY (0x6F)

#define RAM_0_TWOBIT_PARITY (0x6D)

If you ask me, #define RAM_0_ONEBIT_PARITY (0x6F) is an error. The parity value for data 5a5a5a5a with a one bit toggle error should be one of 2d, 2b, 28, 27, 24, 65, 22, 63, 60, 3f, 3c, 7d, 3a, 7b, 78, 36, 74, 72, f, c, 4d, a, 4b, 48, 6, 47, 44, 42, 1e, 5f, 5c, 56, all values in hex, depending on the bit location 0..31 of the toggled bit.

The presented parity value for a two bit error 0x6D I did not verify.

Please be aware that the attached code example is not tested and for educational purposes only. Expect errors and omissions. Do not use it in a real application. Best write and test your own code.

BR

JJack

Show Less

This is a code example which is used to interface the TLE5012B angle sensor in the TLE9879 board. This helps in receiving the angular information about the motor which is present on TLE9879 board. Please look at the pictures attached for configuration details. TLE9879 EVALKIT

Show Less

The code example exemplify the possibility to connect multiple radar sensors with a specific UUID. This helps the user to evaluate the multiple radar sensors simultaneously.

The current code example is demonstrated on BGT60ATR24C and DEMO BGT60TR13C to extract the raw data by connecting the radars with the board specific UUID's using python avian wrapper.

Below is the code snippet for the same.

from ifxAvian import Avian

import numpy as np

#Getting the list of all connected Radar sensors

device=Avian.Device.get_list()

print(device)

#Connecting to a Radar sensor with a specific UUID

dev_BGT60TR13C = Avian.Device(uuid="00313853-314c-4c35-3135-303136303434") #UUID of the board connected with BGT60TR13C

dev_BGT60ATR24C= Avian.Device(uuid="00313853-314c-4c35-3039-303331303237") #UUID of the board connected with BGT60ATR24C

#Setting a full configuration for BGT60TR13C

config_BGT60TR13C = Avian.DeviceConfig(

sample_rate_Hz = 1_000_000, # ADC sample rate of 1MHZ

rx_mask = 7, # activate RX1 and RX3

tx_mask = 1, # activate TX1

if_gain_dB = 33, # gain of 33dB

tx_power_level = 31, # TX power level of 31

start_frequency_Hz = 60e9, # start frequency of chirp: 60GHz

end_frequency_Hz = 61.5e9, # end frequency of chirp: 61.5GHz

num_chirps_per_frame = 64, # 128 chirps per frame

num_samples_per_chirp = 32, # 64 samples per chirp

chirp_repetition_time_s = 0.0005, # 0.5ms

frame_repetition_time_s = 0.2, # 0.2s, frame_Rate = 5Hz

hp_cutoff_Hz = 80_000, # 80kHz cutoff frequency for high-pass filter

aaf_cutoff_Hz = 500_000, # Anti-aliasinf cutoff frequency of 500kHz

mimo_mode = 'off' # MIMO disabled

)

#Setting a full configuration for BGT60ATR24C

config_BGT60ATR24C = Avian.DeviceConfig(

sample_rate_Hz = 1_000_000, # ADC sample rate of 1MHZ

rx_mask = 5, # activate RX1 and RX3

tx_mask = 1, # activate TX1

if_gain_dB = 33, # gain of 33dB

tx_power_level = 31, # TX power level of 31

start_frequency_Hz = 60e9, # start frequency of chirp: 60GHz

end_frequency_Hz = 61.5e9, # end frequency of chirp: 61.5GHz

num_chirps_per_frame = 128, # 128 chirps per frame

num_samples_per_chirp = 64, # 64 samples per chirp

chirp_repetition_time_s = 0.0005, # 0.5ms

frame_repetition_time_s = 0.2, # 0.2s, frame_Rate = 5Hz

hp_cutoff_Hz = 80_000, # 80kHz cutoff frequency for high-pass filter

aaf_cutoff_Hz = 500_000, # Anti-aliasinf cutoff frequency of 500kHz

mimo_mode = 'off' # MIMO disabled

)

dev_BGT60TR13C.set_config(config_BGT60TR13C)

print(dev_BGT60TR13C.get_config())

dev_BGT60ATR24C.set_config(config_BGT60ATR24C)

print(dev_BGT60ATR24C.get_config())

#Printing 10 frames of data for BGT60TR13C

for frame_number in range(10):

print(dev_BGT60TR13C.get_next_frame())

print("Finished printing BGT60TR13C Frames")

#Printing 10 frames of data for BGT60ATR24C

for frame_number in range(10):

print(dev_BGT60ATR24C.get_next_frame())

print("Finished printing BGT60ATR24C Frames")

#Disconnecting the devices

del dev_BGT60TR13C

del dev_BGT60ATR24C

Output

Show Less

Different radar configurations between set of frames are required to enable different kinds of measurements simultaneously.

For example, To have a different number of chirps per frame between the first few frames and the next few frames. Alternatively, when someone requires a specific number of samples per chirp in the first few frames and a different number of samples per chirp in the next few frames.

For instance, if one needs to have 64 samples per chirp for first 10 frames and 256 samples per chirp for the next 10 frames. Or, if one wants first 5 frames to have 16 chirps per frame and next 5 to have 128 chirps per frame.

This code example demonstrates how this can be achieved on DEMO BGT60TR13C radar using Python and ifxAvian Library. Below is a template for the same, and a code example is also attached below.

define config1

define config2

while(...)

{

setConfig(config1)

for(...)

{

get_next_frame()

processFrame()

...}

stop_acquisition()

setConfig(config2)

for(...)

{

get_next_frame()

processFrame()

...}

stop_acquisition()

}

Output: It can be observed in the output on how the max_range and speed_resolution are changing between two sets of frames.

Show Less

This is an example of the 8-bit PCM audio playback on PSoC4200M CY8CKIT-044 Pioneer Board using DMA.

Unlike the previous example, which used an interrupt to update the IDAC, this project is using DMA to transfer the data. This, however, comes with limitation on the audio data size to not exceed 65536 bytes.

The audio data are stored in the PSoC FLASH in 8-bit unsigned PCM format. The IDAC is configured as a Source. The IDAC current is converted into voltage using 3.3k load resistor buffered by the Opamp in the follower mode. For sound generation, the output is directly connected to the headphones with combined impedance of 64oHm (32+32).

The sound starts playing when the onboard switch button (SW2) is pressed, which triggers the DMA transfer. Once all of the data has been played, the sound stops. Subsequent button pressing during the playback restarts the sound wave.

The button events are captured using a ButtonSw32 custom debouncer component, utilizing a WDT0 timer for polling the pins state. The debouncer is set for the external interrupt, and pins state is processed using interrupt callback procedure, automatically clearing the interrupt source. The ButtonSw32 component is included into the project.

Attached project includes several test PCM audio files in 8-bit unsigned format:

sawtooth_8-bit_S.h - test sawtooth, 8-bit, Unsigned (size= 256 bytes)

smb_world_clear_5k5_N_U.h - Super Mario theme, 5.512kHz, Normalized, Unsigned (size=33600 bytes)

smb_world_clear_11kHz_N_U.h - Super Mario theme, 11.025kHz, Normalized, Unsigned (size=65536 bytes)

smb_world_clear_22kHz_U.h - Super Mario theme, 22.05kHz, Unsigned (size=65535 bytes, clipped)

The Super Mario theme produced about 5.5 sec playback with reasonable quality at both 5.5kHz and 11kHz update rate, and about 3 sec at 22.1kHz. No significant differences in audio quality between the samples has been observed. PSoC4 FLASH used was 28% for 5.5kHz files, and 54% for 11kHz and 22kHz files accordingly.

The WAV files have been converted to the C code using WAVtoCode v1.1.1 by Colin Seymour. The original WAV data have been Normalized to fill the entire 8-bit scale, which has increased the dynamic range.

Project attached contains all necessary files. It was tested using both Creator 4.0 and 4.4.

Credits:

WAVtoCode v1.1.1 by Colin Seymour: https://colinjs.com/software.htm#t_WAVToCode

Figure 1. Project schematic. The PCM data are fed from FLASH to the IDAC using chained DMA. The IDAC current is converted into voltage using 3.3k load resistor buffered by the Opamp in the follower mode, producing 0-1V signal at full scale.

Figure 2. DMA chain transfer mechanism. DMA1 is configured to transfer 1 byte of data on each clock from FLASH to the intermediate location in RAM, which is a LSB of the 2-byte CONTROL structure. DMA1 then triggers DMA2, which copies 2 bytes from the CONTROL structure to IDAC_1 control register. The structure of the IDAC_1 control register is shown below.

Figure 3. Custom debouncer component ButtonSw32, which captures SW2 button events and starts the playback.

Figure 4. Project annotation using the PSoC Annotation Library v1.0 and KIT-044. The Opamp output is directly loaded on the headphones with combined impedance of about 64oHm (32+32).

Figure 5. Screenshot of the test sawtooth playback at 5.5kHz. Using 3.3k load resistor, the 0-306uA IDAC range results in 0 to 1V output.

Figure 6. Screenshot of the sample audio playback at 5.5kHz.

This is an example of the 8-bit PCM audio playback using PSoC4200M and CY8CKIT-044 Pioneer Board.

Audio data are stored in the PSoC FLASH in 8-bit signed PCM format, and sent to IDAC on the interrupt at 5.5kHz or 11kHz update rate. The project doesn't use DMA. The IDAC is configured in bidirectional mode (sink and source), corresponding to the sign of the data. The IDAC current is converted into voltage output using an Opamp operating in transimpedance mode. Opamp output is centered around voltage reference Vdd/2.

For sound generation, the output was directly connected to the headphones with combined impedance of 64oHm (32+32).

The sound starts playing when the onboard switch button (SW2) is pressed, which enables the update interrupt. Once all of the data has been played, the sound stops. Pressing the button again during playback restarts it from the beginning.

The button events are captured using a ButtonSw32 custom debouncer component, utilizing a WDT0 timer for polling the pins state. The debouncer is set for the external interrupt, and pins state is processed using interrupt callback procedure, automatically clearing the interrupt source. The ButtonSw32 component is included into the project.

The project includes several test audio files in 8-bit signed format:

sawtooth_8-bit_S.h - test sawtooth

smb_world_clear_5k5_N_S.h -Super Mario theme, 5.512kHz, Normalized, Signed (size=33512 bytes)

smb_world_clear_5k5_ND_S.h - Super Mario theme, 5.512kHz, Normalized and D-compressed (size=33608 bytes)

smb_world_clear_11kHz_N_S.h - Super Mario theme, 11.025kHz, Normalized (size=67064 bytes)

smb_world_clear_11kHz_ND_S.h - Super Mario theme, 11.025kHz, Normalized and D-compressed (size=67064 bytes)

The Super Mario theme produced about 5.5 sec playback with reasonable quality at both 5.5kHz and 11kHz update rate. PSoC4 FLASH used was 28% for 5.5kHz files, and 54% for 11kHz files accordingly.

The WAV files have been converted to the C/H code using WAVtoCode v1.1.1 by Colin Seymour.

The original WAV data have been Normalized to fill the entire 8-bit scale, which increased the dynamic range. For testing purposes some files were additionally D-compressed (log-trimmed) using the BTc SoundEncoder v3.0 by Roman Black, which can further increase the fullness of the sound.

Project attached contains all necessary files. It was tested using both Creator 4.0 and 4.4.

Credits:

WAVtoCode v1.1.1 by Colin Seymour: https://colinjs.com/software.htm#t_WAVToCode

BTc SoundEncoder v3.0 by Roman Black: http://www.talkbotbrain.com/

Figure 1. Project schematic. The PCM data are fed from FLASH to the IDAC on isrTimer interrupt. The IDAC operates in both sink and source modes, updating the mode according to the data sign. The Opamp operates in transimpedance mode with feedback resistor 3.3k, producing +/-1V peak amplitude at full scale around the the reference Vdd/2.

Figure 2. Custom debouncer component ButtonSw32, which captures SW2 button events and starts the playback.

Figure 3. Project annotation using the PSoC Annotation Library v1.0 and KIT-044. The reference voltage Vdd/2 was pulled from the onboard hidden Pin_5[0], reserved for the light sensor. Capacitors C1 and C2 are optional.

Figure 4. Screenshot of the sample audio playback at 5.5kHz.

Figure 5. Screenshot of the test sawtooth playback at 5.5kHz.

Hi,

I am looking for the CY3635 Wireless USB N:1 DVK hub/sensor firmware. I can only find the host software/docs below. I need the PSoC firmware i.e. the .c and .h files.

Show Less

Hi,

Here is my code sample of measuring a pin capacitance using the CapSense component.

I used CY8CKIT-044 but I hope that porting this to ather PSoC 4 which is supporting CapSense won't be difficult.

The key function is "CapSense_GetSensorCapacitance()" which is available only when "Enable self-test library" is checked.

I've used this function a few times before, but as usual I mislocated my code(s).

So this time I decide that to post this sample here will be useful (at least for me).

Schematic

CapSense configuration

[ Basic Tab]

CSD tuning mode : SmartSense (Hardware parameters only)

"SmartSense (Full Auto-Tune)" is not supported for the "self-test library"

[ Advanced Tab]

"Enable self-test library" is checked.

Pins

Note: I used P3[4] which is a built in electrode of CY8CKIT-044

but any pin supported by the CapSense component should work.

Tera Term log

main.c

#include "project.h"

#include "stdio.h"

#define TEXT_LEN 64

char str[TEXT_LEN+1] ;

#define print(s) UART_UartPutString(s)

void cls(void)

{

print("\x1b[2J") ;

CyDelay(100) ;

print("\x1b[;H") ;

CyDelay(100) ;

}

void splash(char *title)

{

cls() ;

snprintf(str, TEXT_LEN, "%s (%s %s)\n\r",title, __DATE__, __TIME__) ;

print(str) ;

}

volatile int sw2_pushed = 0 ;

CY_ISR(sw2_isr)

{

SW2_ClearInterrupt() ;

sw2_pushed = 1 ;

}

void init_hardware(void)

{

CyGlobalIntEnable; /* Enable global interrupts. */

UART_Start() ;

SW2_ClearInterrupt() ;

sw2_int_ClearPending() ;

sw2_int_StartEx(sw2_isr) ;

CapSense_Start() ;

}

void print_measure_error(uint32_t status)

{

switch(status) {

case CapSense_TST_MEASUREMENT_SUCCESS: print("SUCCESS") ; break ;

case CapSense_TST_MEASUREMENT_BAD_PARAM: print("BAD PARAM") ; break ;

case CapSense_TST_MEASUREMENT_LOW_LIMIT: print("LOW LIMIT") ; break ;

case CapSense_TST_MEASUREMENT_HIGH_LIMIT: print("HIGH LIMIT") ; break ;

case CapSense_TST_MEASUREMENT_ERROR: print("Measurement Error") ; break ;

default:

snprintf(str, TEXT_LEN, "Unknown Error: 0x%08X", status) ;

print(str) ;

break ;

}

print("\n\r") ;

}

uint32_t button_cap = 0u ;

void measure_cap(void)

{

CapSense_TST_MEASUREMENT_STATUS_ENUM measurementStatus ;

while(CapSense_NOT_BUSY != CapSense_IsBusy()) {

/* wait for capsence to be free */

}

button_cap = CapSense_GetSensorCapacitance(

CapSense_BUTTON0_WDGT_ID,

CapSense_BUTTON0_SNS0_ID,

&measurementStatus) ;

if (measurementStatus == CapSense_TST_MEASUREMENT_SUCCESS) {

snprintf(str, TEXT_LEN, "capacitance: %d.%03d pF\n\r",

button_cap/1000, button_cap % 1000) ;

print(str) ;

} else {

print_measure_error(measurementStatus) ;

}

}

int main(void)

{

init_hardware() ;

splash("Pin Capacitance Measure Test") ;

print("Push SW2 to measure\n\r") ;

for(;;)

{

if (sw2_pushed) {

sw2_pushed = 0 ;

measure_cap() ;

}

}

}

Some more background

There was a discussion about measuring a pin capacitance.

https://community.infineon.com/t5/PSoC-4/Analog-Digital-pin-control/m-p/455832#M45427

After I posted my sample, I noticed that there was a typo in the comment.

/* wait for capsent to be free */So I wanted to fix it, then I noticed another minor problem which is in case the measurement encounters an error,

the printed error message does not have a new line, so next message will be printed just after that error message.

After all, although basic function has not been changed, some more touch ups were applied from my previous post.

(1) Typo in a comment

(2) New line added after error report

(3) Clear pending pin interrupts before starting the ISR

(4) Some code clean ups

(5) The value was in fF, now shown in pF

(6) Schematic rearranged (no functional changes)

moto

Show Less