- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

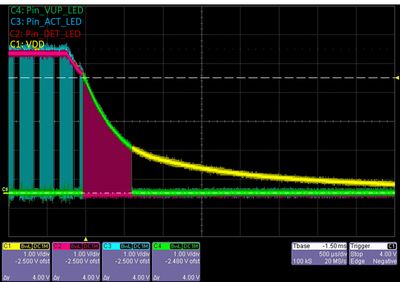

This sample code loops in the LPComp interrupt handler when a low voltage is detected, and stops the application operation below the detected voltage. The CSD operation is performed with Single IDAC, and low voltage detection is performed using another IDAC as the reference voltage of LPComp. It toggles the Pin_ACT_LED pin while scanning the CSD. When a low voltage is detected, the Pin_DET_LED pin is toggled in the LPComp interrupt handler. This low voltage detection causes an interrupt when VDD is about 4.0V or less and executes an infinite loop in the handler, but when VDD exceeds 4.2V, a software reset is executed. Moreover, the Nch MOSFET which accelerates the power consumption of VDD is controlled in order to improve the falling characteristic of VDD when it enters an interrupt.

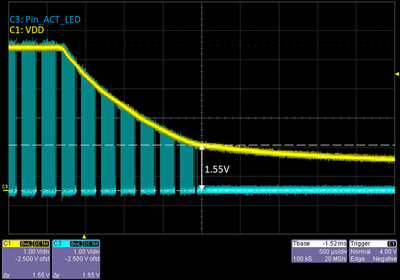

In this waveform, VDD is down while scanning the CSD with the low voltage detection interrupt disabled. As you can see, the code is running even when VDD is about 1.55V. (Please refer to "Power On Reset (PRES)" and "Brown-out Detect (BOD) for VCCD" in the datasheet.)

By applying this code, you can stop the execution of the application when VDD becomes 4.0V or less. And you can also improve the power slew rate of the POR.

However, the best way to stop the application operation is to reset the XRES from the reset IC with the detected voltage.

Best regards,

Yocchi

- Labels:

-

ispn:40040:1:0

-

l1:314:1:0

-

PSoC4MCU