Clocks Forum Discussions

Hello

It would be very helpful if you could answer quickly.

1. I would like to use CY27410 as the CLKBuffer of PCIe. Is there a reference circuit?

2. Regarding the following data sheet, is it necessary to input the same PCIe CLK to the input terminals (IN1, 2) even when using it as a buffer?

Or is it only when using ZDB?

Best Regards

Haya

Show LessWe have recently switched to in-house programming of our clock chips rather than having them pre-programmed by distribution prior to shipment.

My JEDEC file for the CY22381 was created with CyberClocks R3.10.00. When we use this file with our Xeltek SuperPro 7500 programmer we get an error that the "device ID is not correct - programming failed" (see log below)

In speaking with Xeltek they examined the JED file and found no errors. They indicated that they have heard similar reports some other customers and it was resolved after consulting with the IC manufacturer.

I have also regenerated the file with the current version of CyberClocks 3.21.00 and the resulting jedec file is a binary match.

Not sure where to go from here.

08:57:56.627 Loading File X:\CY22381F_BF_Clk.jed

08:57:56.637 0, File Type:Jed, Load mode:0, Buffer offset:0, File offset:0

08:57:56.754 Load File Success!

08:57:56.799 Calculating checksum...

08:57:56.806 Type:Pld

08:57:56.811 Buffer checksum(0):0x00000B65

08:57:56.826 Device Checksum: 0xB65

09:14:51.659 Calculating checksum...

09:14:51.665 Type:Pld

09:14:51.670 Buffer checksum(0):0x00000B65

09:15:37.827 Send PAR...

09:15:38.240 Send PAR OK

09:15:38.247 Send ALGO...

09:15:38.669 Send ALGO OK

09:15:38.676 Send FPGA...

09:15:39.100 Send FPGA OK

09:15:39.111 Send Command

09:15:40.526 Batching...

09:15:40.590 Programming...

09:15:40.735 Device ID doesn't match

09:15:41.317 Program failed!(1)

09:15:41.324 Address:00000000

Chip data:00000000

Buffer data:00000000

Show Less

Hello,

I am currently evaluating the CY2941x/CY2942 for a serdes application and I would need the documentation on how to program it without using the Clock Wizard.

For this application, it is not feasible to use the one-time programming but we need to able to program the chip in mission mode using I2C from a microcontroller.

I have gone through all the documents that I could find on this topic but important pieces are missing. The closest thing I found was the application note "AN210253_CY294xx_High_Performance_Clock_Getting_Started_and_Best_Design_Practices-ApplicationNotes-v03_00-EN.pdf" but it only explains how to do small frequency changes (+/- 500 ppm) and not how to do the "large change" frequency programming.

Where can I find the complete documentation on how to program the large change?

Many thanks in advance,

Best regards

We are considering using CY27410 with the following specifications.

In the case of the following specifications, can it be realized by using one CY27410? Or do you need two?

If it is feasible with one use, please advise about the setting value at that time.

Used as an 11-output clock generator.

Output 1. 156.25MHz LVDS

Output 2. 156.25MHz LVDS

Output 3. 26MHz LVDS

Output 4. 27MHz LVDS

Output 5. 100MHz LVDS

Output 6. 100MHz LVDS

Output 7. 100MHz LVDS

Output 8. 125MHz LVDS

Output 9. 24MHz LVCMOS 1.8V

Output 10. 25MHz LVCMOS 3.3V

Output 11. 25MHz LVCMOS 3.3V

Hi All,

I am using the CY26049-20 as a synchronized clock filtering circuit with with fall back

So I hope to apply a 25MHz ICLK and obtain a 100 MHz phase locked output, and using a 25MHz XTAL input

Obviously I am having some difficulty getting it to function properly

I was wondering if there are any application, layout guide, notes or any data at beyond the basic datasheet for this part. I am using the the -20 par but the only datasheet I can find is the -36 version. so even getting the -20 or generic data sheet would be helpful. Too bad there is no Eval board for this part 🙂

Show Less

I just programmed CY29421FLXI-ND using the clockwizard. When look at each output (single ended) on the scope, i see both clk+ and clk- in sync. Basically clock complement is missing. was there any setting in clockwizard to set the second output as complement of the 1st output one that i missed?

Show Less

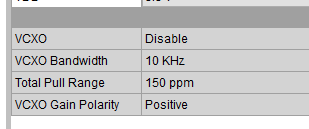

Does CY29421FLXI-ND support VCXO function? i notice it lacks VC pin.

Do I need to disabled this function in clockwizard tool for CY29421FLXI-ND?

Show Less

Hi all,

What are the conditions required by Infineon in term of MOQ for having a factory configured CY2545QI ?

Also, what would be the extra lead time du to this configuration step ?

For instance, the configuration would be :

- 1 output LVCMOS1V8 24MHz

- 1 output LVCMOS1V8 25MHz

- 1 output LVCMOS2V5 100MHz

- 1 output LVCMOS2V5 24MHz

I presume no extra information is required. Am I right ?

Thank you in advance for your support,

Best regards,

Jean-Baptiste

Show LessI am planning to use CY29421FLXI-ND on 3.3V rail, but looks like I2C port is only spec at 2.5V max. is this correct?

Can i pull up I2C signals to 3.3V for this Clock? is it 3.3V tolerant?

Show Less

I need help on how to generate programming file for CY29421FLXI-ND to give to the programming house.

we need to set the following options:

- Output=156.25MHZ

- OE=active low

- Set i2c address

- What tool to use? Where to download?

- What register to write

- and what values?

Thanks

Show Less