Clocks Forum Discussions

Regarding CY27410FLTXI(TRAY) and CY27410FLTXIT(Tape and Reel),

Please let us know TRAY specification and Tape and Reel Specification.

Its Device Package is PG-VQFN-48 (48-Pin QFN (7 × 7 × 1.00 mm) LT48D 5.6 × 5.6 E-Pad (Sawn) Package)

Best regars.

Shigeru Seike /TED

Show Less

Hi all,

I'm writing an IIO driver in C for the Cypress CY22801, with communications via I2C.

However, setting the two available output clock channels generically will be difficult, as there are a lot of variables involved.

For example, I will have to calculate the values for PB, PO, Q, and DIVxN, and select the most suitable divider channel (1/2), and set the source controls for the clock outputs, for each clock output - each will affect the other one, also.

i.e. CLK_OUT_X = (2 * (pb + 4) + po) / (q + 2) / DIVxN * CLK_INPUT_FREQ

The CyClocksRT software generates all of this information automatically. Is the source code for this component of the software available, please? Or can a version of this be provided to aid our use of your products?

Many thanks,

Adam

Show LessHi. I'm looking for the programming interface and adapter to in house program the CY22394. It looks like the Cpress Programming kits are obsolete. Is there a ne one available, or where can I find information on how to program in house.

Thanks

Show LessHi all,

I'm using the CY22801 clock synthesiser on a project with a Xilinx Zynq SoC and Yocto.

I'm developing a C driver and IIO wrapper for use with Linux.

However, I'm not getting a response from the IC via I2C as it seems to be pulling on the SCL line.

Pin 3 (SDAT / FS0 / VCXO / OE / PD# - serial interface data line / frequency select 0 / VCXO analog control voltage / Output Enable / Power-down) and pin 5 (CLKB / FS1 / SCLK - clock output B / frequency select 1 / serial interface clock line) are multi-function pins. How am I supposed to configure this IC for use with I2C?

Many thanks,

Adam

Show LessHello,

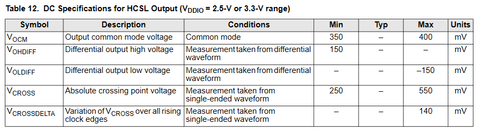

I am trying to use the HCSL output with this clock generator.

The HCSL output specification in the datasheet stated the following:

Let me ask you a few questions about this.

1. There is no single-ended VOH or VOL listed here. What are the HIGH and LOW voltages at single-ended?

2. I understand that the differential voltage amplitude is 300mV (150mV-(-150mV)). Is this correct?

3. If my understanding in 2. is correct, does this voltage meet the HCSL specification?

(For example, the HCSL input specification for CY2DP1502 specifies a differential voltage of 400mV at minimum.)

Please provide an answer.

Regards,

Shimamura

Show LessHi all,

I'm using the CY22801 clock synthesiser on a project with a Xilinx Zynq SoC and Yocto.

I can't find an existing IIO driver in the latest release of the Linux Kernel:

https://elixir.bootlin.com/linux/latest/source/drivers/iio/frequency

Is there a suitable IIO driver that I can use, please?

Failing that, is there a C driver library available that I could integrate into IIO?

Many thanks,

Adam

Show LessHello.

Can I use this crystal for CY27410 ?

P/N: ECS-250-10-36B-CTN-TR

* ECS Inc., ECX-2236B series ( https://ecsxtal.com/ecx-2236b )

* Frequency: 25MHz

* Load Capacitance: 10pF(Specify in P/N)

Is there any replacement (either drop-in or closest) available for the part “CY7B994V-2BBI” or “CY7B994V-2BBIT”

Show LessHello, I was wondering what is needed to reprogram the CY22393. It came programmed with the default serial address of 69H, but I need to change the address to something different for project use. I also have questions on the set up, reading back, it looks like I2C programming can only be used for volatile memory. Will i need to pick up a programmer to reprogram the serial address? Also, any tips and tricks to help me get started with reprogramming the CY22393 device would be greatly appreciated. i couldn't only find posts about this product and my specific issue unless they were from 2008-2009. so i wasnt sure how valid those post still were.

Thanks for the help.

Hello.

I would like to use CY27410 with internal POR, and omit external reset.

Can I leave XRES pin to open?