- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to use the HCSL output with this clock generator.

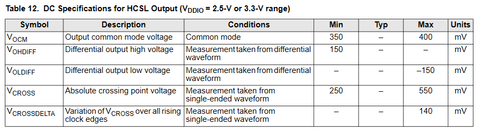

The HCSL output specification in the datasheet stated the following:

Let me ask you a few questions about this.

1. There is no single-ended VOH or VOL listed here. What are the HIGH and LOW voltages at single-ended?

2. I understand that the differential voltage amplitude is 300mV (150mV-(-150mV)). Is this correct?

3. If my understanding in 2. is correct, does this voltage meet the HCSL specification?

(For example, the HCSL input specification for CY2DP1502 specifies a differential voltage of 400mV at minimum.)

Please provide an answer.

Regards,

Shimamura

Solved! Go to Solution.

- Labels:

-

Programmable Clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SuSh_1535366,

We measured the differential pk-to-pk output voltage at our end, and the minimum value measured is -800mV. So, it meets the clock input of FPGA differential voltage min value = 350mV.

Hence, you can use CY27410 in your application.

Below is the measurement snapshot for reference:

Thanks,

Ritwick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SuSh_1535366,

Regarding (2) & (3), are you looking for the below spec? Kindly confirm.

Regarding (1), I will check internally and will update you in my next response.

Thanks,

Ritwick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ritwic,

Thank you for your answer.

I want to use the OUT13 of the CY27410 as HCSL output for a GTP transceiver clock for the Xilinx Artix-7 FPGA.

The clock input of this FPGA requires a minimum of 350mV as differential voltage.

Could CY27410 be used for this application?

Regards,

Shimamura

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SuSh_1535366,

Apologies for the delay. Since the data is unavailable in the datasheet, we need to measure it. For this, we need some input from your side on the operating conditions. Kindly let us know.

- VDDIO voltage

- Output frequency (Fout)

- Temperature conditions (if any)

Thanks,

Ritwick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ritwick,

Thanks for the reply.

Please wait a moment as we will check and respond to your question about the condition you asked about.

Regards,

Shimamura

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ritwick,

I will answer your question below:

1. VDDIO voltage -> VDDIO_D:3.3V VDDIO_S:1.8V

2. Output frequency ->100MHz

3. Temperature conditions -> 60℃ max.

Regards,

Shimamura

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SuSh_1535366,

We measured the differential pk-to-pk output voltage at our end, and the minimum value measured is -800mV. So, it meets the clock input of FPGA differential voltage min value = 350mV.

Hence, you can use CY27410 in your application.

Below is the measurement snapshot for reference:

Thanks,

Ritwick