AURIX™ Forum Discussions

Hello,

I get a KIT_A2G_TC387_5V_TFT and use the "AURIX_code_examples-master\code_examples\SPI_TLF_1_KIT_TC397_TFT" demo code want to debug the SPI, but after bulid shows "ctc E498: Vector table numbers are not allowed for TriCore "tc1.3"", what should I do fot this?

Thank you!

Show LessDear Aurix users,

I have a question about ECC mechanism in TC23x device.

As far as I know, ECC can correct one bit error in data read (DSPR).

Can ECC correct one bit error in data write (DSPR)?

Show LessHello Community,

I m working on a Vector FBL on Tc3E7 and i m trying to communicate with an SBC using QSPI4.

I configured the Baudrate to 500000 and the fQSPI to 160Mhz.

I m using Mcal SPI driver.

using the logic analyzer(screenshot below), I saw that the clock is sent out with the correct frequency, the MOSI data is correct, the chipselect is also triggered correctly and there is data returned from SBC in the MISO line.

However, the SPI does not read the data in MISO line and returns FFFFF intead.

Do you have any hints what could be the issue here ?

Show Less

What are the MTU SSH instances of TC334 and where should I obtain them

Hi,

we are testing on prototypes with TC299 TX using ATI vision.

Later we will migrate to TC299 TP without EMEM.

Will there be difference in performance between the 299 TP and 299 TX?

I think there will be some due to EMEM is located in LMU?

Best regards, Charles

Show Less

Hello,

I'm trying to find the offset of an SRC for TC38x. For TC27x, these were listed in "Table 16-4 Registers Overview - Service Request Control Registers" but I appreciate this mechanism has changed for TC3XX to an SRC Index Number.

The TC3XX user manual gives an example in 16.5.1 as follows:

•- SRC_BCU_SPB offset is 20Hex (see Chapter 16.13)

- Index(SRC_BCU_SPB) = 20Hex / 4 = 8

However chapter 16.13 does not explain how the offset for SRC_BCU_SPB (SRC_BCUSPB) is 0x20 nor for any other module.

Does anybody know where these offsets are listed please?

Thank you very much.

Show LessCan two TC boards of different make i.e TC297 and TC375 be connected to the same PC and be switched through them when required to use ? Lauterbach is used to connect the hardware to the PC.

Simultaneously both won't be in use. Only 1 board at a given time will be in use.

[Curious: Can both boards be in use simultaneously? ]

Thanks! Show Less

hello everyone,

I want to ask a question about OVC of TC397.

Setting Description:

I use multicore of TC397.The target adress is in PF4. The OVC redirection address is LMU(0xBxxxxxxx).The Cache(DCache and PCache) of each core is enable in startup. The OVC of each core is enable by core0. and each section is set by core0.DCINVAL is set to 1 by core 0. In a word, every setting about OVC is set by core0.

Var_A is a const variable in my target adress and redirection adress is LMU(0xBxxxxxxx),Var_B and Var_C are common variable. I use XCP to change Var_A in core0, use (Var_B = Var_A) in core0, use (Var_C = Var_A) in core4.

Error Description:

Var_B is changed with Var_C,but Var_C is not and keep init value.

Then I do some test,the result is that the DCache of core4 must be bypass,regardless the Dcache of Core 0 is enable or bypass, both Var_B and Var_C can be changed with var_A.

But in my project ,I must enable Dcache of each core to improve performance.

What can I do to make OVC work in the situation of making DCache of each core enable.

thank you

Show Less

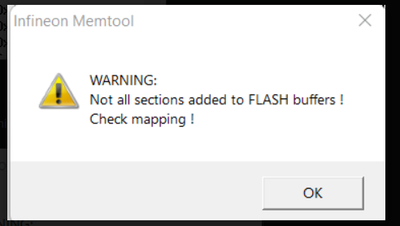

Hi

I created a TC37x project with ADS and right now using Tasking compiler for my TC375 lite kit.

Am using SSW to call main function (right now I have no user code in my project, just the auto generated files from ADS)

Also am using the linker script generated from ADS and the memory looks something like this

When am trying to flash the hex files using memtool am getting this warning and need help to sort this out

Thanks

Show Less