AURIX™ Forum Discussions

text.format{('custom.tabs.no.results')}

I wonder how to use DSADC, TIM and MCS to do peak&hold control for GDI system and which aspects should pay attention to?

Thanks and regards,

Lina

#8042000 13236 Show Less

When using a camera with 8 parallel data ports to access the CIF, should the correspondence look like this?

Camera_D0-->CIF_D8

Camera_D1-->CIF_D9

Camera_D2-->CIF_D10

Camera_D3-->CIF_D11

Camera_D4-->CIF_D12

Camera_D5-->CIF_D13

Camera_D6-->CIF_D14

Camera_D7-->CIF_D15

Because I noticed that in the CIF driver there is as defined in the diagram。

If an 8-bit parallel data port camera is used, it will append 8 MSBs or Zeros as LSBs, which leads to the fact that when 8 data ports of the camera are connected to the low 8 LSBs of the CIF, data will be overwritten anyway if you want to use the sub-ISP functions correctly. And if only raw data is transferred(no sub-Cif function used), correspondence of connections does not matter。

The above is my understanding, is it correct?

Thank you!

Show LessHi, I started to work on basic set of configurations for Aurix TC277. I am using CCU6 to generate PWM for space vector modulation. I took demo software called CCU6_PWM_Generation_1_KIT_TC297_TFT and based on this software I made mine. Everything would work fine but I have noticed that dead time is not generated at all. I am guessing that it is not configured right. Where should I look for initial settings ...or any example to save some time on studying. Thank you in advance for any help with it. Good luck in your projects with Aurix chip! Robert

I got it resolved because it is very simple. There is one register to set one dead time value for all 3 legs of inverter at once. It needs to be set once after reset and it works fine ...I did not check whether it can be changed easily later ...but I guess it should be doable any time ...

Show Less

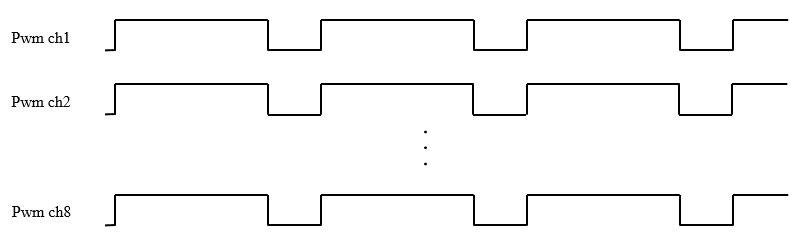

I want to try out the phase shift full bridge control with the following three features.

Can you provide me with a sample or method to simply check them?

1. Outputs 8 channels of pwm

We think it is possible to add the ATOM channel of the previously tried sample.

Do you have any concerns when considering No. 2 and 3?

*https://www.infineonforums.com/threa...tion-Kit-TC3x7

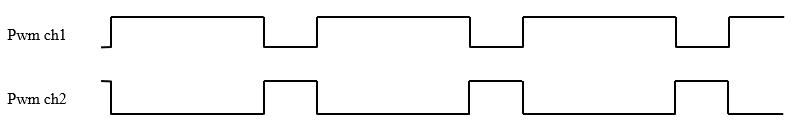

2.Output the pwm inversion signal.

I think it's possible to achieve this by using a dead-time module.

Is there sample code available for reference to use the DTM?

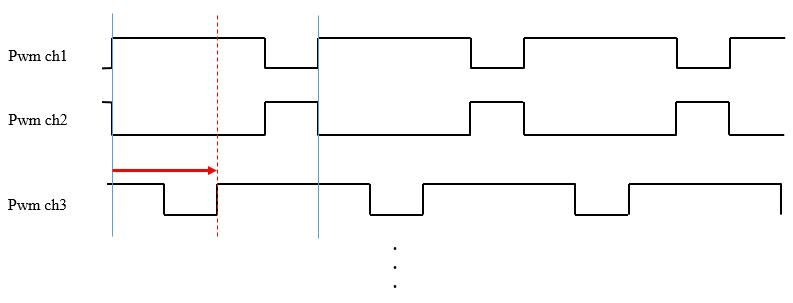

3.Output phase-shifted pwm

The CCU6 would make this happen, but there are only three units, CC60-CC62.

If you want to combine No.1 and 2 to achieve this with 4 phase x 2 channels, could you please tell me how to achieve the same function with GTM?

Thanks, Show Less

I have been trying to use iLLD module in order to initialize CAN controller to send some data out on our custom board with TC322. I'm using example code from infineon for to cofigure CAN controller. The problem i'm facing is that, according to datasheet MCR (Module Control Register) needs to be initialize in particular sequence. Like MCR.CCCE and MCR.CI is cleared then at one point, we have to wait for MCR.RBUSY to be 0 to make sure that RAM initialization is completed.

In example code for TC334, initModule is supposed to be initialize controller but i do not see this bit being checked. During debugging, it is supposed to sending data out but micro-controller is not sending anything on on TX pin.

Anyone faced similar case ? Can anybody help me in this case ?

Show LessHi,

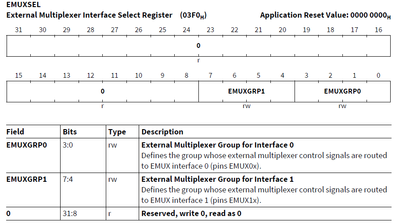

I am now working on ADC emux function, and I have a question about the meaning of EMUXSEL.

I have two questions.

1.

For example, if I write 8 to EMUXGRP1, what is the number of 8 for?

2.

From the TC3xx user manual p1240, there is some descriptions as follow:

Each available EMUX control interface can be controlled by an arbitrary group (see register EMUXSEL). One

channel or a set of channels from that group can be selected for this operating mode (see register GxEMUXCS

(x=0-11)).

In my opinion, the group is the two emux group, and the channels in emux group can be choosed. Am I right?

Show LessHello,

I am using TC364 and getting OVC working for CAL data page overlay. Just using CPU0 at present

I configure a single OVC block to overlay PFLASH from Sector 8 with LMU RAM from Sector 9.

Before the switch I write some data into the overlay RAM for a test. Then I switch on the overlay. RABRx.OVEN is clear but all other fields in RABRx OMASKx and OTARx are setup. OVCENABLE is already enabled for CPU0. OSEL.SHOVEN is set - ready to enable the OVC block. Then I write to OVCCON to switch on OVC.

Then repeat reads from the PFLASH addresses and LMU RAM addresses.

The first read from PFLASH address range gets the value left in PFLASH. The second read and all further reads from PFLASH address range gets the value from LMU RAM as expected.

I have tried using cached and non cached address ranges (0x8000 0000 or 0xA000 0000 for PFLASH and 0x9000 0000 or 0xB000 0000 for LMU RAM). I get the same result in both cases.

If I add 2 dsyncs after the write to OVCCON to switch I get the expected data on the first read after the switch (value from RAM not PFLASH). Sometimes 1 dsync is enough, but not always !

Can anyone help me understand why the first data read is getting the value from PFLASH not the overlaid LMU RAM please.

Also for calibration data pages is it generally better to avoid cached areas ?

I will try to read into Tricore cache coherency and have looked at other OVC related posts.

Many thanks

Show LessI'm new to the Aurix/Tricore and was wondering if there is an example of how to effectively use the MCMCAN module as a hardware gateway that can receive a message on one node and automatically transfer and transmit on another node. In our previous projects we used an XMC for this functionality and it worked great. We are now targeting the TC33x and trying to work out something similar.

The datasheet mentions automatic transferring of messages in section 40.3.1.6.1, but it didn't provide much information.

Any ideas on how to go about it?

Thanks!

Show LessHi Everyone,

Following the ADS (AURIX Developer Studio). I have configured EDSADC (TC38A) in singled ended mode using P004 as input. And I tried to obtain the result, but output value (raw adc value) is always 0xFFEA ~ 0xFFE3 and it is not varying even if the input signal is varied.

Can you please check the attached EDSADC driver initialization/configuration, especially EDSADC Pin configuration (which is not present in ADS Documentation). And please give me your feedback whether the initialization/configuration is correct or not.

Thanks,

EthanHunt.

Show Less