AURIX™ Forum Discussions

Hello, everyone

I am attempting to utilize the GTM module to generate a trigger signal for the EDSADC. My objective is to synchronize multiple EDSADCs by utilizing this trigger signal. However, I am facing challenges while configuring the GTM and EDSADC. I have included the relevant code below, and I would greatly appreciate any hints or guidance you can provide to resolve these issues.

void initGtmAtom(void)

{

IfxGtm_enable(&MODULE_GTM); /* Enable GTM */

IfxGtm_Atom_Timer_Config timerConfig; /* Timer configuration structure */

IfxGtm_Atom_Timer_initConfig(&timerConfig, &MODULE_GTM); /* Initialize default parameters */

timerConfig.atom = IfxGtm_Atom_0; /* Select the ATOM_0 */

timerConfig.timerChannel = IfxGtm_Atom_Ch_0; /* Select channel 0 */

timerConfig.clock = IfxGtm_Cmu_Clk_0; /* Select the CMU clock 0 */

timerConfig.base.frequency = ATOM_FREQ; /* Set timer frequency */

timerConfig.base.isrPriority = ISR_PRIORITY_ATOM; /* Set interrupt priority */

timerConfig.base.isrProvider = IfxSrc_Tos_cpu0; /* Set interrupt provider */

timerConfig.triggerOut = ;

IfxGtm_Cmu_setClkFrequency(&MODULE_GTM, IfxGtm_Cmu_Clk_0, CMU_FREQ); /* Set the clock frequency */

IfxGtm_Cmu_enableClocks(&MODULE_GTM, IFXGTM_CMU_CLKEN_CLK0); /* Enable the CMU clock 0 */

IfxGtm_Atom_Timer_init(&g_timerDriver, &timerConfig); /* Initialize the ATOM */

IfxGtm_Atom_Timer_run(&g_timerDriver); /* Start the ATOM */

}and

IfxEdsadc_Edsadc_ChannelConfig edsadcChannelConfig; /* Channel configuration structure */

/* Initialize the configuration with default values */

IfxEdsadc_Edsadc_initChannelConfig(&edsadcChannelConfig, &g_edsadc1);

/* Configure the comb filter */

edsadcChannelConfig.combFilter.decimationFactor = DECIMATION_FACTOR; /* Set the decimation factor */

edsadcChannelConfig.combFilter.startValue = START_VALUE; /* Set the starting value of the decimation counter */

/* Configure the FIR filters in the filter chain */

edsadcChannelConfig.firFilter.prefilterEnabled = TRUE; /* Enable the Pre-Filter in the filter chain */

edsadcChannelConfig.firFilter.fir0Enabled = TRUE; /* Enable the FIR0 Filter in the filter chain */

edsadcChannelConfig.firFilter.fir1Enabled = TRUE; /* Enable the FIR1 Filter in the filter chain */

edsadcChannelConfig.firFilter.calibrationTrigger = TRUE; /* Start the calibration initializing the channel */

/* Configure the modulator */

edsadcChannelConfig.modulator.modulatorClockFreq = MODULATOR_FREQ; /* Set the modulator frequency */

edsadcChannelConfig.modulator.negativeInput = IfxEdsadc_InputConfig_referenceGround; /* Set single-ended mode */

edsadcChannelConfig.channelId = (IfxEdsadc_ChannelId)AN2_CH0; /* Select the channel to configure */

edsadcChannelConfig.cicShift = CICSHIFT; /* Set the CIC shift */

edsadcChannelConfig.gainFactor = GAINFACTOR; /* Set the gain factor */

/* Set the intended full-scale value */

edsadcChannelConfig.gainCalibrationConfig.calTarget = RAW_FULL_SCALE;

edsadcChannelConfig.demodulator.triggerInput = IfxEdsadc_TriggerInput_b;

IfxEdsadc_Edsadc_initChannel(&g_edsadc1Channel1, &edsadcChannelConfig); /* Initialize the channel */

IfxEdsadc_Edsadc_startScan(&g_edsadc1, MODULATOR_MASK, CHANNEL_MASK); /* Start scan with modulator 0, chn 0 */

I believe that the configuration of the EDSADC channel is correct, and I have set the trigger input to 'GTM EDSADC Trigger 1.' However, I am unable to locate the corresponding configurations in the GTM module for the 'timerConfig.triggerOut' setting.

Thank you inadvance~

Best regards,

Zheng Tao

Show LessHello,

I have a problem using Global Interrupt between AURIX Tricore TC234x and C167CR.

According to iLLD of TC23A:

+ IfxCpu_enableInterrupts -> to enable the global interrupt

+ IfxCpu_disableInterrupts -> to disable the global interrupt

However, there is no information about which bits are Set or Clear to enable/disable global interrupt. The final line I found is:

"extern void __enable( void) __attribute__((intrinsic_function(0x103, 0, "enable") ));" (which cannot go further)

As compared to C167CR, its reference manual states that:

+ In PSW register: Set/Clear bit IEN to enable/disable the interrupt correspondingly, while we cannot do that in the Tricore TC23x.

My question is that:

+ Is it equivalent to use IfxCpu_enableInterrupts and IfxCpu_disableInterrupts functions in Tricore TC23x instead of Set or Clear IEN bit in PSW register in C167CR?

Best regards

Show Lesshi:

使用例程I2C_Read_Ext_Device_1_KIT_TC397_TFT 通过I2C读写EEPEOM时,读取时没有问题 ,#define ADDRESS_OF_MAC_ADDRESS 0xF2 根据此地址可以读出LAN 的MAC地址,在写时流程如下:

#define ADDRESS_OF_MAC_ADDRESS 0x100;

uint8 i2cTxBuffer[LENGTH_OF_ADDRESS] = {ADDRESS_OF_MAC_ADDRESS};

uint8 i2cTxBuffer_writedata[LENGTH_OF_ADDRESS] = {0x66};

while(IfxI2c_I2c_write(&g_i2cDevEeprom, &i2cTxBuffer[0], LENGTH_OF_ADDRESS) == IfxI2c_I2c_Status_nak);

while(IfxI2c_I2c_write(&g_i2cDevEeprom, &i2cTxBuffer_writedata[0], LENGTH_OF_ADDRESS) == IfxI2c_I2c_Status_nak);

/* Read the unique MAC address */

while(IfxI2c_I2c_read(&g_i2cDevEeprom, &g_macAddr[0], LENGTH_OF_MAC_ADDRESS) == IfxI2c_I2c_Status_nak);

把0x66数据写到EEProm 内部地址为0x100的位置,读出数据为0xff,应该是没有写进去。

请问对通过I2C对EEProm如何进行写data?

多谢!

Show LessI'm currently using TC277 Application kit and ADS 1.9.8

I am new here.

Everytime I debug my codes, I see this.

At the very first start of the program, it works fine but after a few of restart or reset the target or other operations it happens.

They also say in 'registers' I have to refresh view but have no idea how to do.

Can any one give me a hint? Thanks in advance.

Show Less

In my project, when I connect the debugger, the software will enter Trap (Trap Class 4, TIN2). The program runs normally when the debugger is not connected

From the Trap information, I know that it is a LBE(Load Bus Error) error, but I still do not know when this trap will occur.

At the time of the trap, the program is initializing Ram, copying data from rom to ram.

But the strange thing is that each time a trap occurs, the while loop is different, sometimes 500 cycles, sometimes 1000 cycles.

The trap that occurs when you run the following code. Can someone take a look at this for me? Thank you very much.

Show Less

Hi Infineon team,

For gigabit ethernet connectivity, We are planning to interface SAK-TC397XX-256F300S BD MCU with KSZ9897R PHY chip via the RGMII interface. Could you please clarify on the following queries?

KSZ9897R Data Sheet (microchip.com)

1. Since the ethernet switch chip complies with RGMII 2.0 standard, Can we expect the MCU chip to recognize the switch/PHY out of the box provided RGMII interface is enabled and PHY address is configured?

Our understanding is we can use the pre-existing software implementation for RGMII with minimal or no changes. Please confirm.

2. We noted in the EVM (KITA2GTC3975VTRBSTOBO1) that the GREFCLK pin of the MCU chip is connected to CLKOUT of the PHY chip. Is this connection necessary? Does this signal need length matching with RGMII RX group(input to MCU) in the PCB?

3. Could you please share information on tested PHY/switch chips with this MCU if available?

Thanks,

Balaji

Hi, i am developing a TC387QP system. The supply mode is :

details are VEXT and VEVRSB use 5V extertal, VFlex and VDDP3 use 3.3V extertal, VDD use EVRC in SMPS mode.

I have tested GPIO and PWM function, the port is 5V level,but I want a 3.3V level. How can i implement it?

Show LessHI,

it exsist a library (or something like that ... the best is free source code) for the TCP/IP managing and easily

portable on a AURIX DEVELOPMENT TOOL project?

Thanks

Fabio

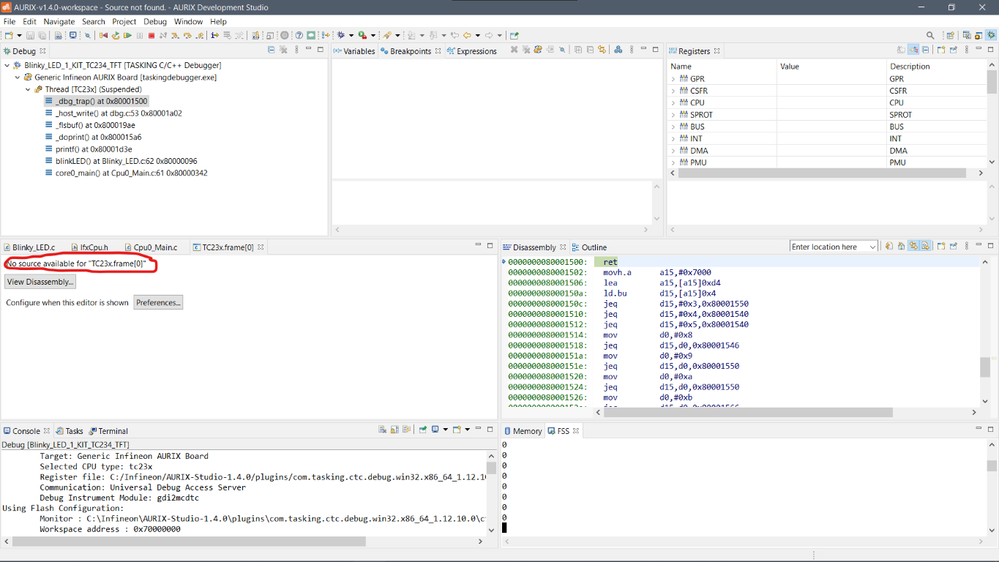

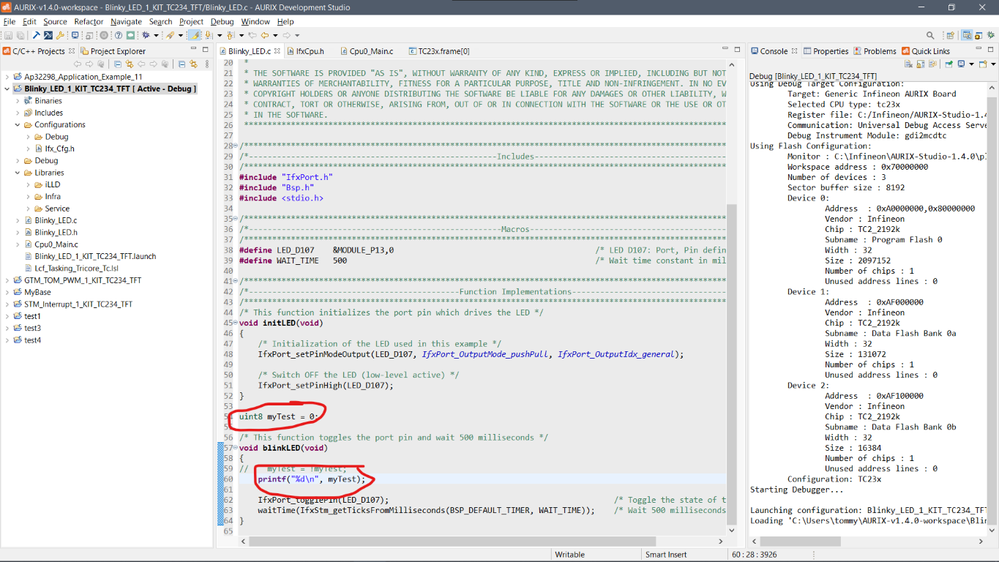

Show LessI am using AURIX Dev. Studio and was testing printf() to print out variable to FSS window. At first it work fine, but after a while (~1min) the program will halt suddenly and a window will pop out saying "No source available for "TC23x.frame[0]"". The disassembly point to a function called _dbg_trap() but I can't find it anywhere in source code.

I have even tried replacing iLLD with V1.0.1.13.0 but still no use.

I have attached some screenshots here. I have also uploaded my project for examination. The project is just the demo project Blinky_LED_1_KIT_TC234_TFT with 2 line added in Blinky_LED.c to keep printing out variable myTest when LED is toggled. You can download it here: https://1drv.ms/u/s!ArYO_KxP91FxgZdETkoIB3ZM9abwGg?e=0iM0tR

Thanks for reading, any reply is appreciated.

Show Less

Show Less