AURIX™ Forum Discussions

AURIX™

Hello Support,According to User Manual Revision 1.4 for Aurix 2G, SMU_AGi [0-11] -- SMU Alarm Status Registers [Offset 1C0H+i*4] are supposed to be cl...

Show More

Hello Support,

According to User Manual Revision 1.4 for Aurix 2G, SMU_AGi [0-11] -- SMU Alarm Status Registers [Offset 1C0H+i*4] are supposed to be cleared to zero upon Application Reset.

Can you please confirm whether these registers are indeed cleared upon Application Reset/Lauterbach Target Reset?

For my Triboard, I see AG0/AG1/AG2/AG3 as 0x2490 upon Target Reset.

Best Regards Show Less

According to User Manual Revision 1.4 for Aurix 2G, SMU_AGi [0-11] -- SMU Alarm Status Registers [Offset 1C0H+i*4] are supposed to be cleared to zero upon Application Reset.

Can you please confirm whether these registers are indeed cleared upon Application Reset/Lauterbach Target Reset?

For my Triboard, I see AG0/AG1/AG2/AG3 as 0x2490 upon Target Reset.

Best Regards Show Less

AURIX™

Looking for a way to help others and be rewarded for it? By simply sharing your knowledge at our AURIX™ Forum, you can win a special prize!How does it...

Show More

Looking for a way to help others and be rewarded for it?

By simply sharing your knowledge at our AURIX™ Forum, you can win a special prize!

How does it work?

1. Complete and submit the registration form. Entrants into the prize draw shall be deemed to have accepted the Terms & Conditions.

2. Your name will then automatically be assigned to the participation list.

3. At the end of each quarter, our expert panel will select the winners based on your scores. The scores are based on the level of engagement as reflected in the number of comments, threads, likes, shares and replies.

4. Winners will be notified by email in the second week of the following quarter.

Click here to sign up for the AURIX™ Forum competition! Show Less

By simply sharing your knowledge at our AURIX™ Forum, you can win a special prize!

How does it work?

1. Complete and submit the registration form. Entrants into the prize draw shall be deemed to have accepted the Terms & Conditions.

2. Your name will then automatically be assigned to the participation list.

3. At the end of each quarter, our expert panel will select the winners based on your scores. The scores are based on the level of engagement as reflected in the number of comments, threads, likes, shares and replies.

4. Winners will be notified by email in the second week of the following quarter.

Click here to sign up for the AURIX™ Forum competition! Show Less

AURIX™

Hello,Is there any sample code for DSADC Offset and gain calibration implementation in TC277xDC/TC299xBC ?I can't find the one in iLLD and no applicat...

Show More

Hello,

Is there any sample code for DSADC Offset and gain calibration implementation in TC277xDC/TC299xBC ?

I can't find the one in iLLD and no application note also in myICP.

Best Regards,

Naresh Show Less

Is there any sample code for DSADC Offset and gain calibration implementation in TC277xDC/TC299xBC ?

I can't find the one in iLLD and no application note also in myICP.

Best Regards,

Naresh Show Less

AURIX™

Hi,i am using TC39x-BB, MCAL V1.30, Tresos V23. My Problem is by following Implementation /* REMS (Read Electronic & Device ID) */ SpiCmd[0u] = ...

Show More

Hi,

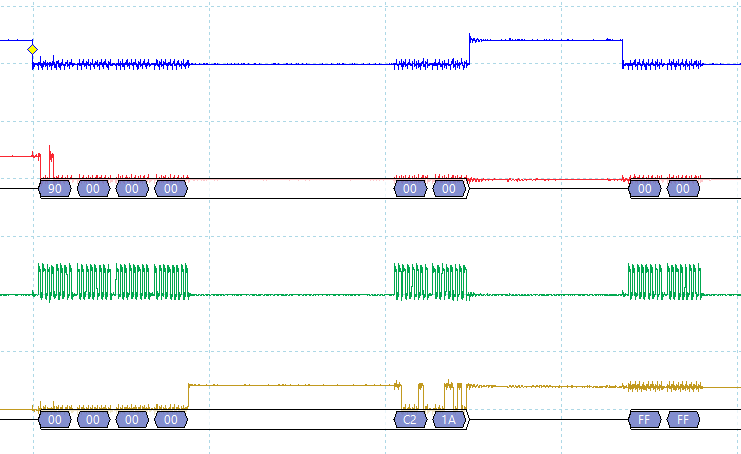

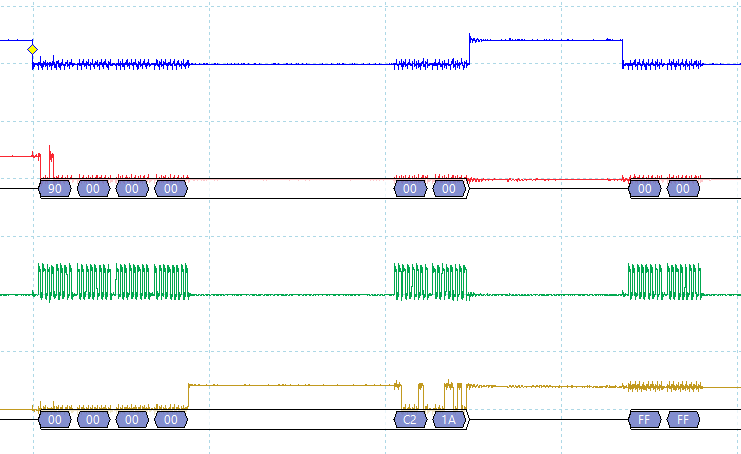

i am using TC39x-BB, MCAL V1.30, Tresos V23. My Problem is by following Implementation

I am getting all the 6 Bytes data in SpiCmdRcv instead of 4 Bytes data in SpiCmd and 2 Bytes Data in SFLS__DeviceIdentification. Could you please let me know is there any known bug known in Mcal version 1.30? or is it a configuration issue?

I am expecting the 4 Byte „00 00 00 00“ in SpiCmdRcv and next two Bytes „C2 1A“ in SFLS__DeviceIdentification. But if I make SpiCmdRcv 8 Bytes large then i receive all the 8 Bytes „00 00 00 00 C2 1A FF FF“ in SpiCmdRcv. I am unable to understand why is it so?

Thank you in advance!

BR

Usman Show Less

i am using TC39x-BB, MCAL V1.30, Tresos V23. My Problem is by following Implementation

/* REMS (Read Electronic & Device ID) */

SpiCmd[0u] = SFLS_RegCommand_REMS_CMD;

SFLS__SpiSeqEndFlag = SFLS_SpiSeqMode_ACTIVE;

Spi_SetupEB(SpiConf_SpiChannel_FLASH_CMD_CH, SpiCmd, SpiCmdRcv, 4u);

Spi_SetupEB(SpiConf_SpiChannel_FLASH_DATA_CH, NULL_PTR, (Spi_DataType*)&SFLS__DeviceIdentification, 2u);

Spi_AsyncTransmit(SpiConf_SpiSequence_FLASH_DATA_SEQ);

I am getting all the 6 Bytes data in SpiCmdRcv instead of 4 Bytes data in SpiCmd and 2 Bytes Data in SFLS__DeviceIdentification. Could you please let me know is there any known bug known in Mcal version 1.30? or is it a configuration issue?

I am expecting the 4 Byte „00 00 00 00“ in SpiCmdRcv and next two Bytes „C2 1A“ in SFLS__DeviceIdentification. But if I make SpiCmdRcv 8 Bytes large then i receive all the 8 Bytes „00 00 00 00 C2 1A FF FF“ in SpiCmdRcv. I am unable to understand why is it so?

Thank you in advance!

BR

Usman Show Less

AURIX™

I didn’t receive any help, so solved already.

AURIX™

Hi,

is there any Ada compiler for AURIX TriCore? What about run time environment support? (e.g. ZFP, Ravenscar)

is there any Ada compiler for AURIX TriCore? What about run time environment support? (e.g. ZFP, Ravenscar)

AURIX™

Hi,we have working standard CAN for 500 Kbps, now we are developing CAN FD on top it for Micro Controller (SAL TC264 D).These are the changes made in...

Show More

Hi,

we have working standard CAN for 500 Kbps, now we are developing CAN FD on top it for Micro Controller (SAL TC264 D).

These are the changes made in CAN FD:

1. FDEN bit was set in control register,

2. Set Nominal baudarate for 1 Mbps and fast baudrate for 2 Mbps was configured,

3. In Message object function control register, Message Mode Control selected to : 5 "CANFD 64 bytes message mode",

4. BRS ans FDF was enabled,

After making these, the CAN-FD was not working and getting Passive Error and i have doubt on Bottom and Top Pointer in Message Object FIFO/Gateway pointer, which message object(It has 255 message objects) should use to send complete 64 bytes of data .

Please let me know, any changes need to be done, Show Less

we have working standard CAN for 500 Kbps, now we are developing CAN FD on top it for Micro Controller (SAL TC264 D).

These are the changes made in CAN FD:

1. FDEN bit was set in control register,

2. Set Nominal baudarate for 1 Mbps and fast baudrate for 2 Mbps was configured,

3. In Message object function control register, Message Mode Control selected to : 5 "CANFD 64 bytes message mode",

4. BRS ans FDF was enabled,

After making these, the CAN-FD was not working and getting Passive Error and i have doubt on Bottom and Top Pointer in Message Object FIFO/Gateway pointer, which message object(It has 255 message objects) should use to send complete 64 bytes of data .

Please let me know, any changes need to be done, Show Less

AURIX™

(Board: TriBoard TC3x7 TH V2.01)Hi,referencing the 3xx Manual 44.3.9.5.2, it should be possible to route a packet based on the destination address to ...

Show More

(Board: TriBoard TC3x7 TH V2.01)

Hi,

referencing the 3xx Manual 44.3.9.5.2, it should be possible to route a packet based on the destination address to a spedific DMA channel.

There should be DCS set with (0x1 for e.g. DMA channel 1) of the specific MAC Address register - if the DA of the packet matches, it should be routed to DMA channel 1.

Also the Q0DDMACH of the MTL_RXQ_DMA_MAP0 should be set to 0x1.

But with this config the packets remain in Q0. Anything else needed?

Is there a special Hw_Feature needed?

PS: The static mapping with Q0MDMACH to channel 1 works fine.

Thanks,

Greetings Show Less

Hi,

referencing the 3xx Manual 44.3.9.5.2, it should be possible to route a packet based on the destination address to a spedific DMA channel.

There should be DCS set with (0x1 for e.g. DMA channel 1) of the specific MAC Address register - if the DA of the packet matches, it should be routed to DMA channel 1.

Also the Q0DDMACH of the MTL_RXQ_DMA_MAP0 should be set to 0x1.

But with this config the packets remain in Q0. Anything else needed?

Is there a special Hw_Feature needed?

PS: The static mapping with Q0MDMACH to channel 1 works fine.

Thanks,

Greetings Show Less

AURIX™

Hi,i created a project with the Bifaces multiple .elf example, which works fine.Based on that, i would like to use the same source files for condition...

Show More

Hi,

i created a project with the Bifaces multiple .elf example, which works fine.

Based on that, i would like to use the same source files for conditional compiling for e.g. 2 seperate elf files , how would you setup this in the .xml config file with the correspondant definitions as compiler flag

to build those two elf with one build initiation?

Greetings Show Less

i created a project with the Bifaces multiple .elf example, which works fine.

Based on that, i would like to use the same source files for conditional compiling for e.g. 2 seperate elf files , how would you setup this in the .xml config file with the correspondant definitions as compiler flag

to build those two elf with one build initiation?

Greetings Show Less

AURIX™

Hello to everybody,Do anyone knows which AURIX toolchain can be used to "build, edit and customize" the sw source code provided with the "Hybrid Kit D...

Show More

Hello to everybody,

Do anyone knows which AURIX toolchain can be used to "build, edit and customize" the sw source code provided with the "Hybrid Kit Drive (Sense)"?

Could be the Aurix Development Studio, HighTec IDE, Tasking VX or some other 3rd party tool?

I suppose that those sw source code are related to the examples and funcionalities described in the app. notes:

1) Infineon-AN_HybridKit Drive Quickstart Manual-AN-v01_01-EN.pdf

https://www.infineon.com/dgdl/Infineon-AN_HybridKit%20Drive%20Quickstart%20Manual-AN-v01_01-EN.pdf?fileId=5546d4625f96303e015fde4e83b32835

and

2) Infineon-Hybrid Kit Drive - Advanced Features of Evaluation Kit for HybridPack Drive-AN-v01_01-EN.pdf

https://www.infineon.com/dgdl/Infineon-Hybrid%20Kit%20Drive%20-%20Advanced%20Features%20of%20Evaluation%20Kit%20for%20HybridPack%20Drive-AN-v01_01-EN.pdf?fileId=5546d4625f2e26bc015f4e1c6f2c13f8

Thanks in advance,

Stefano Show Less

Do anyone knows which AURIX toolchain can be used to "build, edit and customize" the sw source code provided with the "Hybrid Kit Drive (Sense)"?

Could be the Aurix Development Studio, HighTec IDE, Tasking VX or some other 3rd party tool?

I suppose that those sw source code are related to the examples and funcionalities described in the app. notes:

1) Infineon-AN_HybridKit Drive Quickstart Manual-AN-v01_01-EN.pdf

https://www.infineon.com/dgdl/Infineon-AN_HybridKit%20Drive%20Quickstart%20Manual-AN-v01_01-EN.pdf?fileId=5546d4625f96303e015fde4e83b32835

and

2) Infineon-Hybrid Kit Drive - Advanced Features of Evaluation Kit for HybridPack Drive-AN-v01_01-EN.pdf

https://www.infineon.com/dgdl/Infineon-Hybrid%20Kit%20Drive%20-%20Advanced%20Features%20of%20Evaluation%20Kit%20for%20HybridPack%20Drive-AN-v01_01-EN.pdf?fileId=5546d4625f2e26bc015f4e1c6f2c13f8

Thanks in advance,

Stefano Show Less

Forum Information

AURIX™

In this forum you can post your questions, comments and feedback about the 32-bit AURIX™ TriCore™ Microcontroller. The AURIX™ offers the highest scalability in performance, memory & peripherals across application. It is a safe and secure companion chip, meeting both the ISO functional safety standards and EVITA full security standards. Here you can also find the links to the latest board pages, SW and Tools GitHub, trainings, documents and FAQs

Important links

Overview

Documentations

Others

Related Forums

Trending discussions