- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I know that UCB_SWAP and UCB_OTP can do the proper work of SOTA .I can also use SCU_STMEM1 to get the current SOTA status .

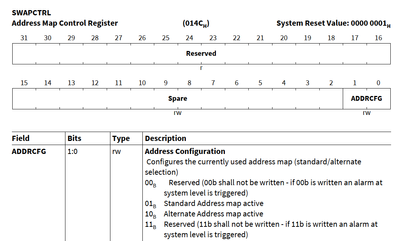

But I don't know what SRU_SWAPCTRL.ADDRCFG ?

I have several questions?

1. The UCB saves the SOTA configuration information. After the system is reset, the SOTA configuration information is saved in SCU_STMEM1. When do YOU need to operate SRU_SWAPCTRL.ADDRCFG

2. The wrong operation SRU_SWAPCTRL. ADDRCFG will trigger ALARM. When should I operate this register and what should I do if an error is triggered

Thanks

Solved! Go to Solution.

- Labels:

-

AURIX

- Tags:

- SOTA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

SRU_SWAPCTRL is supposed to be only read by the user, SSW writes to this register based on the swap configuration. User can read the register to know the current active bank which is similar to SCU_STMEM1.SWAP_CFG.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

SRU_SWAPCTRL is supposed to be only read by the user, SSW writes to this register based on the swap configuration. User can read the register to know the current active bank which is similar to SCU_STMEM1.SWAP_CFG.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How does SOTA work with SMU?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

After enable SOTA, if SRC_SWAPCTRL.ADDRCFG set to wrong value(00b&11b),the ALM11[13] will trigger in SMU, user can configure the SMU generate an interrupt request to any of the CPUs or an reset request or an FSP output.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are right, but I don't need to operate SRC_SWAPCTRL.ADDRCFG to start SOTA. Under what circumstances should SRC_SWAPCTRL.ADDRCFG write data?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After enable SOTA, if you want change start Bank(A or B ),you need write a new data in UCB_SWAP_ORIG.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks.

You are right. I want to know is whenSRU_SWAPCTRL.ADDRCFG is used, not UCB_SWAP_ORIG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

when update new programs , customer use the SCU_SWAPCTRL.ADDRCFG bits to determine whether the system in the standard or alternate address map, and from it, derives which are the 'active' and 'inactive' PFLASH banks. customer can program new software to 'inactive' PFLASH.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks.

I can obtain the activation status from the read-only register SCU_STMEM1.SWAP_CFG.

SRU_SWAPCTRL.ADDRCFG is readable and writable, I should write to SRU_SWAPCTRL.ADDRCFG at the right time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

In the user manual, you can find the write attribute for SRU_SWAPCTRL register is ST i.e. Access only when startup (SSW) executes. So, SRU_SWAPCTRL is meant to be written only by SSW. You will get an error when the application code writes to this register.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the user manual, write attribute for SRU_SWAPCTRL register is ST i.e. Access only when startup (SSW) executes.

I would like to know how SRU_SWAPCTRL.ADDRCFG is configured to work with SMU ?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

use SCU_SWAPCTRL verifying the installed memory address map of SCU_STMEM1 register.

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the user manual, write attribute for SRU_SWAPCTRL register is ST i.e. Access only when startup (SSW) executes.

I would like to know how SRU_SWAPCTRL.ADDRCFG is configured to work with SMU ?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

SMU alarm gets triggered if the SRU_SWAPCTRL.ADDRCFG has reserved value due to bit flip.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello:

SRU_SWAPCTRL.ADDRCFG can only write during SSW, which is in the STARTUP stage of MCU, and there is no jump to user code at this time. When will I receive this error, and how should I deal with it after I receive this error? If it fails, MCU will be locked. In addition, SSW is the program at the startup stage of MCU, how to modify this part of the program?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Yes, only SSW can write to the register. But considering functional safety, we need to identify bit flip (due to radiation, etc.) in critical register and take action. You may need to reset the device to bring it back to safety.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello:

SSW should be the code running before ifx_sSW_tc0.c. How can I modify this part of the code so that I can catch this fault?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

This fault detection is always enabled automatically, you need to configure SMU and take action.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

SMU works in the user program, SRU_SWAPCTRL.ADDRCFG can only be written during SSW, SSW will enter the user program after completing the normal startup process. If the wrong UCB is written to the SRU_SWAPCTRL.ADDRCFG during SSW, the user program is not in use at this time, SMU has not been started, and the wrong UCB is written to the SRU_SWAPCTRL.ADDRCFG during SSW will result in a permanent lock of the chip. I think there is a contradiction between their implementation. Can you elaborate on their relationship?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

SSW does only valid SWAP configuration, this mechanism mainly targets random faults in hardware rather than the systematic fault.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

SRU_SWAPCTRL.ADDRCFG can only be written during SSW. If the user incorrectly configits, his SMU failure will not be obtained by the user, and the user will not be able to take remedial measures for this failure, but will only let the chip enter the permanent lock state.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

By 'user incorrectly configits', do you mean the UCB_SWAP_ORIG_MARKERLx has invalid value? In such a case, SSW doesn't configure SRU_SWAPCTRL at all and there is no alarm. It is responsibility of user to program valid UCB_SWAP_ORIG_MARKERLx in the UCBs.

Thanks.