- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

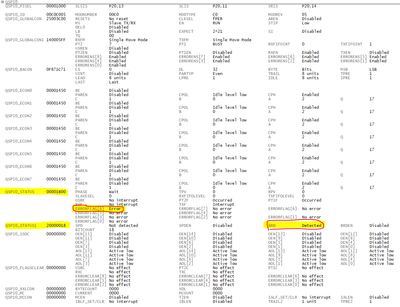

I am implementing QSPI Slave. During power up, I am seeing BRD (Baud Rate Deviation) flag being set for sometime and also ERRORFLAG[8]: SLSI misplaced inactivation (slave mode) being set as shown in the below 1st picture. I am not able to understand why BRD being set.

Not able to understand what is causing this issue on slave.

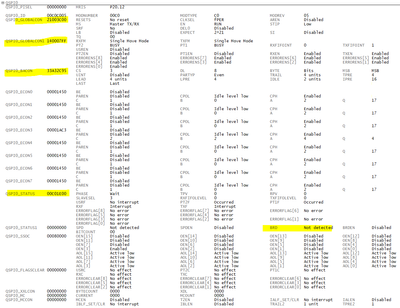

I checked the Master QSPI registers as shown in below picture and I couldn't find any root-cause.

This happens only for sometime (depending on Master's frame transmission period) after that BRD flag resets and SLAVE is sending/receiving data properly, but ERRORFLAG8 still being set.

Any one has an idea of what is going here.. I got stuck here and really appreciate your help..

Thank you

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As per screenshots, i assume you are using QSPI0 Chip Select 3. There is a change of QSPI0_ECON3 Register value in figure 1 and 2. you need to configure the slave select, baudrate and so on. prior to Tx-RX functionality.

Have a look at following example specially the initalization part:

AURIX_code_examples/code_examples/SPI_TLF_1_KIT_TC397_TFT at master · Infineon/AURIX_code_examples (...

BR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For ERRORFLAGS[8], means SLSI misplaced inactivation (slave mode)

For BRD, means Baud Rate Deviation Flag, shows if baud rate deviation has been detected.

Write of 1 sets the bit and raises the event per software. Write of 0 has no effect.

0B no event

1B event detected

Please refer to 37.3.3.2 Shift Clock Monitoring in AURIXTC3XX_um_part2_v2.0.pdf:

Spike detection reacts immediately, baud rate detection requires several bits with higher baud rate. Baud rate detection uses a window two nominal bit times wide and counts the real bit times: double baud rate error requires at least four real shift clock pulses to be detected, triple baud rate error requires six and so on.

Baud rate detection does not react to all spikes smaller than one kernel clock period.In case of too low baud rate,

baud rate error detection reacts immediately, spike detection ignores this case.

So, it's suggested to check if your SPI master has random baud rate change.

OR, you could check data length and baud rate divider settings as below description in the manual:

In slave mode, the module simply immediately responds to external clock edges. Therefore, the settings for the leading, trailing, idle delays, and duty cycle and sampling point are irrelevant. From all timing settings, only the data length and the baud rate divider setting are relevant. The baud rate setting is important because of its role of watchdog timer of the incoming serial clock.

dw

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Di_W Thank you very much for your reply. Is there any little more insight to the error flag8 (misplaced inactivation: slave mode). What does it mean by this? I couldn't find any more details in the Data sheet other than just name of the error flag.

Can I understand it as "Slave received its SLSI deactivation (meaning Chip select gets to high) from Master while Slave transmission is in progress?"

Thank You

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I think your understanding is right.

dw