- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good Morning,

Would someone please explain why we have 8 identical DATAENTRY registers per QSPI Module? I am working on TC364D. If I want to transfer data from Master to a Slave which one among the 8 DATAENTRY registers should I use on MASTER and SLAVE?

For example, can I use any one of the DATAENTRY registers (DATAENTRY0 or DATAENTRY1 or ...... DATAENTRY7) ?

(or)

Is this depends on the SlaveSelect Channel?

Thank you

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

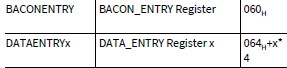

The BACONENTRY and DATAENTRYx are virtual registers (meaning they do not hold any data they only serve to route a write from these registers to the TXFIFO). When writing these registers you still have to respect the TXFIFO fill level. You can refer to Figure 489 Using Tx FIFO Mix and Bacon / Data Entries. When using the LONG mode to send bytes the QSPI expects the data to be packed (you must write 32-bits at a time) and on the last write if you have less than four bytes to send it will only send the remaining amount as indicated by DL. Note the QSPI will send the Most Significate Byte first in the word that you write.

For example lets say you want to send 6 bytes, you set the DL=5 and the first word=0x03020100, the second word is 0x00000504. you will see on the bus 0x030201000504.

Having multiple DATAENTRYx registers allow you to set up small buffers where the first entry is always the BACONENTRY. Then you can use a DMA channel to move the BACONENTRY followed by up to 8 DATAENTRYx registers. With the destination pointer using a simple increment by a word after each movement.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This does not depend on the slave select. You can refer to the "long" and "continuous" data mode transmissions in the section "37.3.5.1 Transmit and Receive FIFOs" section in "AURIXTC3XX_um_part2_v2.0.pdf" where multiple DATAENTRY registers are used.

Best Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Nambi Appreciate your feedback. It makes sense now.

I have been trying to use Long transmission mode (LAST = 1, BYTE=1, DL=23) to transmit 24bytes in one frame but it was not working. As I update DATAENTRY0~DATAENTRY5 (4 x 32-bits), it is working.

Would you provide feedback on below questions, please

- So, for Short Transmission mode, we can just use DATAENTRY0 (or MIXENTRY) for the transmission, correct?

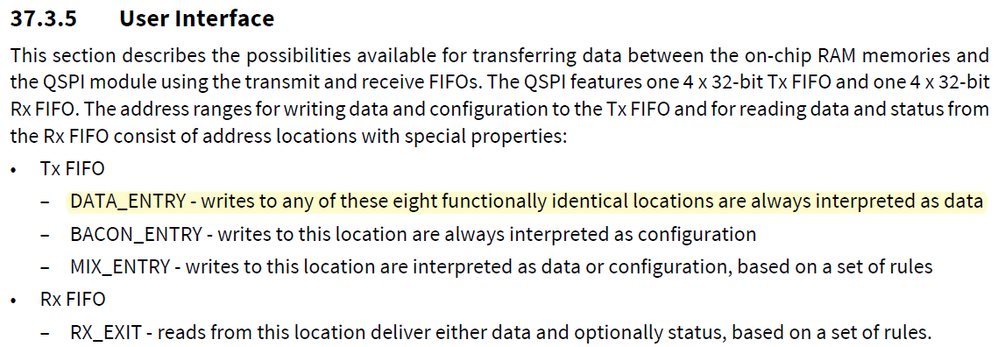

- Also, could you please provide a small screen shot or point me to the paragraph that explained these details about the purpose of having eight DATANETRY registers? I am referring to "AURIXTC3XX_um_part2_v1.4.pdf" but, I couldn't figure out where these details are explained. I can see (below screenshot) Long Data Mode provide max of 32bytes in the below paragraph, but it doesn't explain how you can achieve that 32bytes. Event from the picture below this paragraph "User Interface in Long Data Mode", it is not clear, because the picture also depicts just "DATAENTRY"...not "DATAENTRY0 or DATAENTRY1" etc..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The BACONENTRY and DATAENTRYx are virtual registers (meaning they do not hold any data they only serve to route a write from these registers to the TXFIFO). When writing these registers you still have to respect the TXFIFO fill level. You can refer to Figure 489 Using Tx FIFO Mix and Bacon / Data Entries. When using the LONG mode to send bytes the QSPI expects the data to be packed (you must write 32-bits at a time) and on the last write if you have less than four bytes to send it will only send the remaining amount as indicated by DL. Note the QSPI will send the Most Significate Byte first in the word that you write.

For example lets say you want to send 6 bytes, you set the DL=5 and the first word=0x03020100, the second word is 0x00000504. you will see on the bus 0x030201000504.

Having multiple DATAENTRYx registers allow you to set up small buffers where the first entry is always the BACONENTRY. Then you can use a DMA channel to move the BACONENTRY followed by up to 8 DATAENTRYx registers. With the destination pointer using a simple increment by a word after each movement.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content