May 21, 2020

08:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May 21, 2020

08:42 AM

Hello Support,

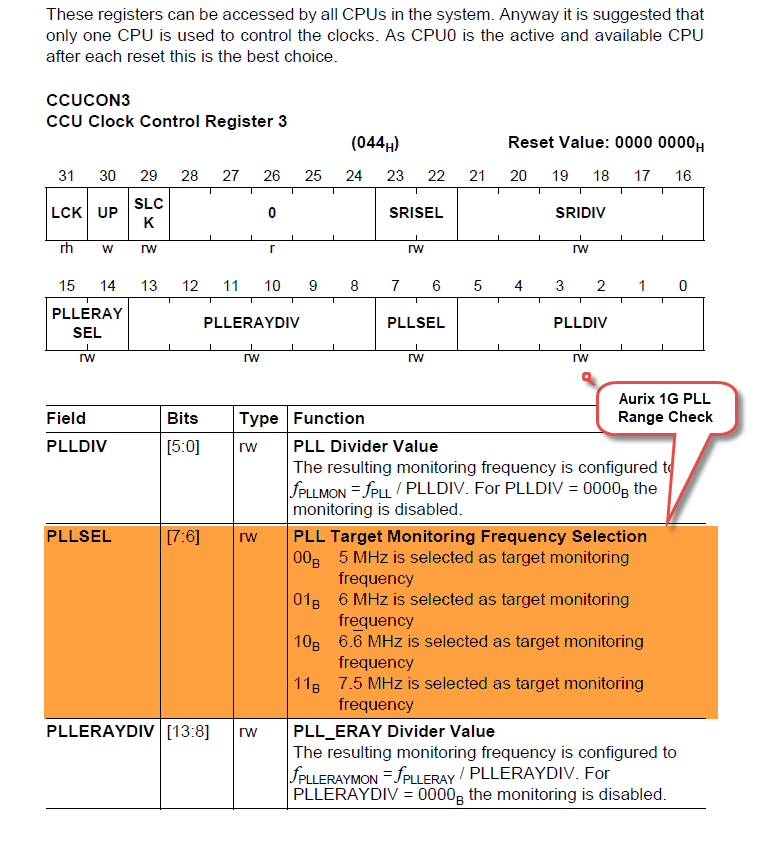

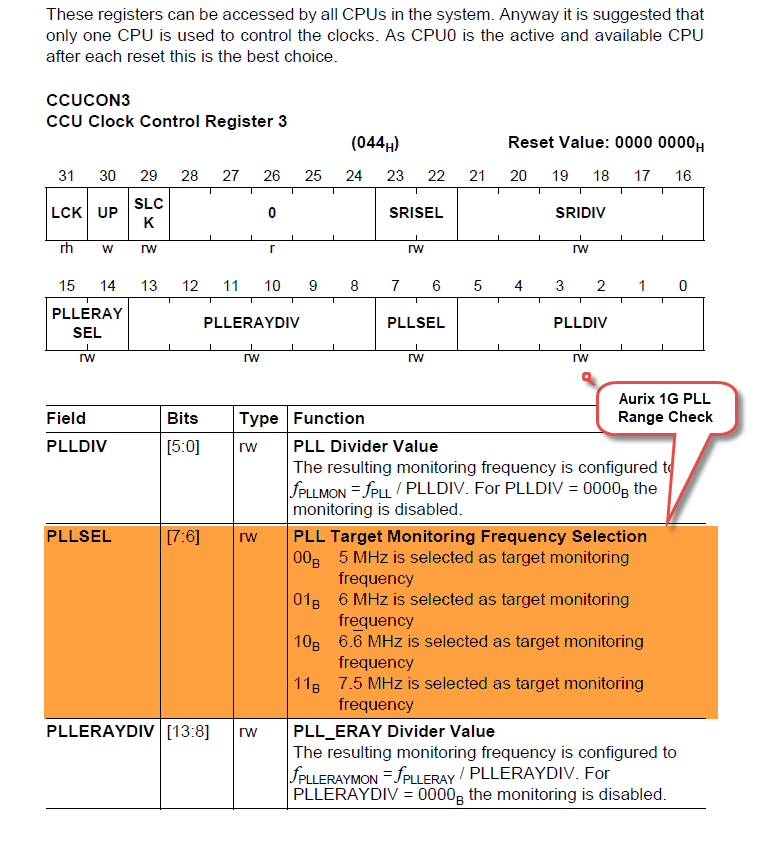

In Aurix 1G, there was PLL output range monitoring as shown below.

Is there any way one can implement fPLL0 range monitoring in Aurix 2G internally within the IC without any external circuit?

May be there is an internal loopback possible within the Aurix 2G and user can measure the frequency using GTM.

Any help about fPLL0 range monitoring related info will help.

fPLL0 Clock Alive monitoring is only implemented in Aurix 2G via CCUCON3 register.

There is no Aurix 1G like PLL range monitoring I could find.

Best Regards

In Aurix 1G, there was PLL output range monitoring as shown below.

Is there any way one can implement fPLL0 range monitoring in Aurix 2G internally within the IC without any external circuit?

May be there is an internal loopback possible within the Aurix 2G and user can measure the frequency using GTM.

Any help about fPLL0 range monitoring related info will help.

fPLL0 Clock Alive monitoring is only implemented in Aurix 2G via CCUCON3 register.

There is no Aurix 1G like PLL range monitoring I could find.

Best Regards

- Tags:

- IFX

5 Replies

May 21, 2020

09:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May 21, 2020

09:32 AM

It's different on TC2xx. See 7.1.5 Clock Monitors. That's generally handled by the MCAL and tested for latent faults at startup with SafeTlib.

May 21, 2020

09:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May 21, 2020

09:42 AM

Hello Support,

For Aurix 1G, I understood PLL range monitoring without any issue.

I was asking for similar feature of PLL range monitoring either indirectly or directly for checking fPLL0 range within Aurix 2G device.

Can you please provide me some clue about how to check for 300MHz fPLL0 within the Aurix 2G without any external output clock signal measurement?

Let me know if the question is not clear enough.

Best Regards

For Aurix 1G, I understood PLL range monitoring without any issue.

I was asking for similar feature of PLL range monitoring either indirectly or directly for checking fPLL0 range within Aurix 2G device.

Can you please provide me some clue about how to check for 300MHz fPLL0 within the Aurix 2G without any external output clock signal measurement?

Let me know if the question is not clear enough.

Best Regards

May 21, 2020

09:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May 21, 2020

09:56 AM

The fBACK alarm range test limits in CCUCON4.UPTHR and LOTHR ensure that both fBACK and fPLL0 are correct.

May 21, 2020

11:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May 21, 2020

11:12 AM

Hello Support,

That is what I thought initially.

But looks like it will not detect.

Assume fPLL0=300MHz for which UPTHR and LOTHR are configured correctly.

Now, suppose in the failure mode, fPLL0 drops to 100MHz, CCUCON0.CLKSEL=0 is the way I am testing, then the threshold values will not catch this error.

That's what I am finding after running the software.

Let me know if you are able to test it under the above mentioned condition.

Best Regards

That is what I thought initially.

But looks like it will not detect.

Assume fPLL0=300MHz for which UPTHR and LOTHR are configured correctly.

Now, suppose in the failure mode, fPLL0 drops to 100MHz, CCUCON0.CLKSEL=0 is the way I am testing, then the threshold values will not catch this error.

That's what I am finding after running the software.

Let me know if you are able to test it under the above mentioned condition.

Best Regards

May 21, 2020

11:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May 21, 2020

11:53 AM

Correct: because of the dividers, not all errors will be caught. That is one reason the Safety Manual lists 3.3.4 External Time-Window Watchdog as a Top Level Safety Requirement.