- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kumaresh. Is this for TC2xx? If so, the incorrect value in DMA RDCRC for 8- and 16-bit transfers is a known issue - see DMA_TC.039 in the errata sheet. The erratum was fixed in TC3xx.

DMA_TC.039 Read Data CRC

The Read Data CRC (RDCRC) calculates an IEEE 802.3 ethernet CRC32 checksum as DMA moves read data through the DMA. The DMA implementation of the algorithm does not zero extend the read data for SDTB (8-bit) and SDTH (16-bit) accesses resulting in the calculation of a wrong checksum value.

The RDCRC must only be used with STDW (32-bit), SDTD (64-bit), BTR2 (128-bit) and BTR4 (256-bit) access sizes. It must be noted that SDTD, BTR2 and BTR4 are only supported for SRI-source to SRI-destination transactions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In FCE, the bit width of each word should be in terms of KERNEL polynomial width.

You would need to pad the 16-bit data.

Please find the thread below:

https://community.infineon.com/t5/AURIX/Calculated-CRC-from-FCE-on-the-DMA-data-being-transferred-do...

Regards,

Aiswarya.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, If I pad other 16 bits to the data which I need to calculate CRC using FCE then it will be different by the CRC calculated by DMA. Does the padded bits also considered in CRC calculation? From my testing I see that the CRC is computed with padded bits. So thought to confirm with you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kumaresh. Is this for TC2xx? If so, the incorrect value in DMA RDCRC for 8- and 16-bit transfers is a known issue - see DMA_TC.039 in the errata sheet. The erratum was fixed in TC3xx.

DMA_TC.039 Read Data CRC

The Read Data CRC (RDCRC) calculates an IEEE 802.3 ethernet CRC32 checksum as DMA moves read data through the DMA. The DMA implementation of the algorithm does not zero extend the read data for SDTB (8-bit) and SDTH (16-bit) accesses resulting in the calculation of a wrong checksum value.

The RDCRC must only be used with STDW (32-bit), SDTD (64-bit), BTR2 (128-bit) and BTR4 (256-bit) access sizes. It must be noted that SDTD, BTR2 and BTR4 are only supported for SRI-source to SRI-destination transactions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I observe this behaviour in TC377

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

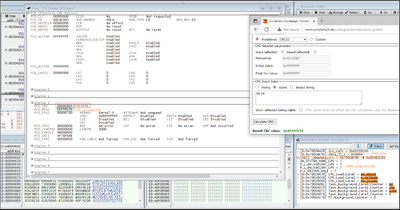

Could you please share the complete data stream fed to DMA and the FCE engine?

Kind Regards,

Aiswarya.