- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

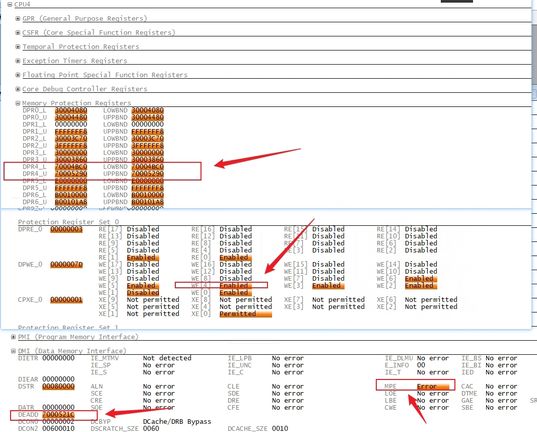

Recentlly, I'm using AURIX TC397's MPU,

I config 7 data MPU regions for each cpu(core0 ~ core5), for core4, protection set 0, region 4 is Write enable,

however, when I debug the program, it run into MPW trap, and DEADD register indicate 0x7000521C is violate the MPW

( I'm sure that SYSCON.PROTEN is set and PSW.PRS is set0)

My question is: 0x7000521C is between [0x70004BC0, 0x70005290) , why it occur trap 1? does this reasonable?

( ps: this phenomenon also happen in core5 when I debug another time )

Solved! Go to Solution.

- Tags:

- memory protection

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks, this problem is solved.

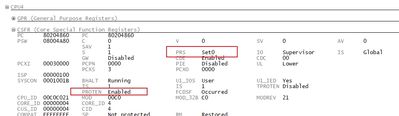

i saw PRS is set0 when trap occur, actually it is Set2 before trap.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MPE Memory Protection Error : Data access violating memory protection.

First please remove all the protection to try, then try to focus if Read Error or Write Error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

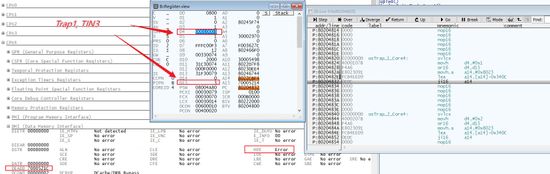

At the very beginning, the program runs OK, and i think it is a Write Error

i debug by sigle step, when it run st16.b [a15]0x8, d15, it occur trap, and 0x7000521C is a global varible

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please remove the protection? Could you please confirm enabled read and write for protection set 0, region 4?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

---1, at the very beginning, I didn't config any MPU region , and the program runs OK.

---2, i change the region 4 's read permiss to enable, but it seems no difference

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks, this problem is solved.

i saw PRS is set0 when trap occur, actually it is Set2 before trap.