Apr 28, 2020

05:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Apr 28, 2020

05:30 AM

Hello Support,

Can you please tell me the reason and solution for the following SMU alarm?

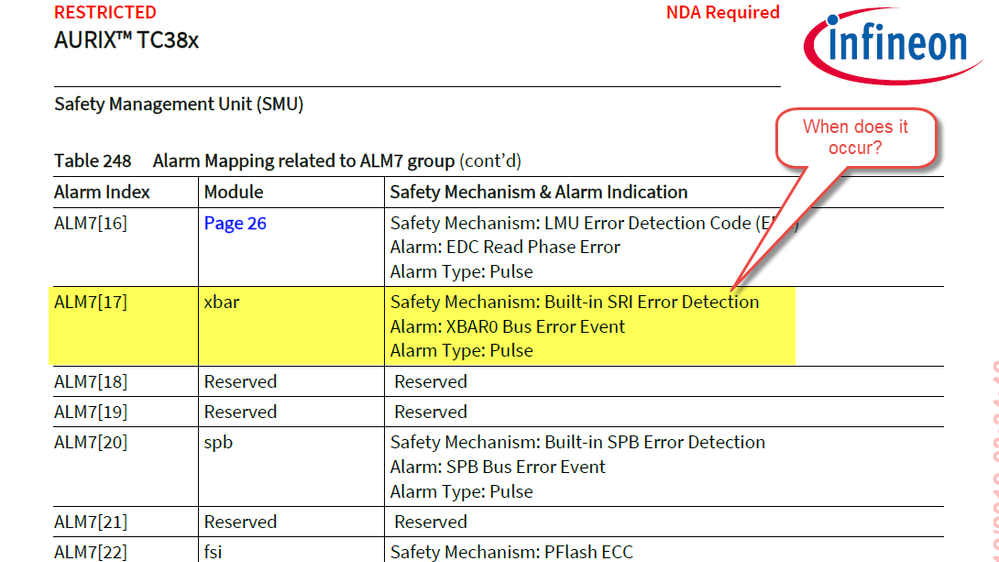

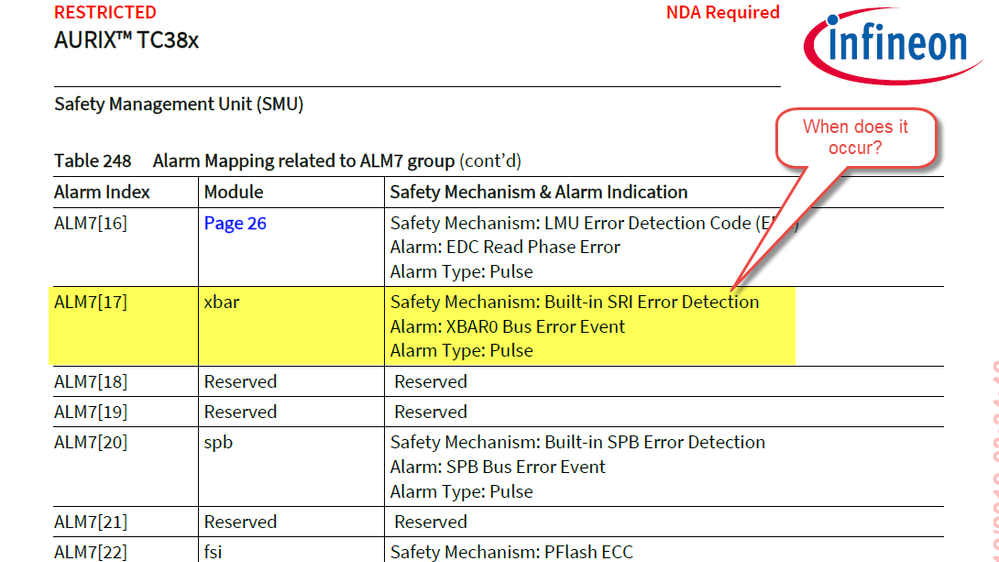

XBAR0 Bus Error Event -- ALM17[17] in Aurix 2G device.

Best Regards

Can you please tell me the reason and solution for the following SMU alarm?

XBAR0 Bus Error Event -- ALM17[17] in Aurix 2G device.

Best Regards

- Tags:

- IFX

2 Replies

Apr 28, 2020

05:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Apr 28, 2020

05:49 AM

For the possible reasons, see 4.3.3.1 SRI Protocol Errors and 4.3.3.2 SRI Transaction ID Errors in AURIXTC3XX_um_part1_v1.4.pdf.

The solution is application dependent. My general advice is:

- Configure the SMU alarm reaction to NMI

- Within the NMI handler, log the error to RAM that is preserved across resets, then cause a software reset

- If the same error occurs three consecutive times, do something appropriate (some sort of "limp home" reduced functionality or permanent error state)

The solution is application dependent. My general advice is:

- Configure the SMU alarm reaction to NMI

- Within the NMI handler, log the error to RAM that is preserved across resets, then cause a software reset

- If the same error occurs three consecutive times, do something appropriate (some sort of "limp home" reduced functionality or permanent error state)

May 04, 2020

12:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May 04, 2020

12:26 AM

The alarm is generated by any transaction which triggered a bus error, and the bus error could be for any reason, so for example, a register location with no mapped register, access protection error, user privilege error, or if you injected an ECC error to test the safety mechanism,

To solve the alarm, you will need to establish which instruction was triggering the error. The XBAR logs the cause of the error into its status registers, so once the alarm has happened, read these to find the address of the transaction and the source master (via the tag).

To solve the alarm, you will need to establish which instruction was triggering the error. The XBAR logs the cause of the error into its status registers, so once the alarm has happened, read these to find the address of the transaction and the source master (via the tag).