#### AN90799

# PSoC® 4 Interrupts

Author: Rajiv Badiger

**Associated Project: Code Examples**

Associated Part Family: All PSoC 4 Parts

Software Version: PSoC Creator™ 3.3 or later

To get the latest version of this application note, please visit http://www.cypress.com/AN90799.

AN90799 explains the interrupt architecture in PSoC 4 and its configuration in PSoC Creator™. This document serves as a guide in developing interrupt-based projects. Advanced interrupt concepts such as latency, vector selection, interrupt code optimization, and debug techniques are also explained.

#### **Contents**

| 1 | Intr | oduction                                | 1  | 7.2                 | Interrupt Latency                   | 15 |

|---|------|-----------------------------------------|----|---------------------|-------------------------------------|----|

| 2 | PSo  | oC 4 Interrupt Architecture             | 2  | 7.3                 | Optimizing the Interrupt Code       | 16 |

|   | 2.1  | Interrupt Sources                       | 2  | 7.4                 | Components with Inbuilt Interrupts  | 16 |

|   | 2.2  | Level- and Edge-Triggered Interrupts    | 4  | 7.5                 | Forcing the Interrupt Vector Number | 17 |

| 3 | Inte | errupt Support in PSoC Creator          | 5  | 7.6                 | SysTick Timer                       | 18 |

|   | 3.1  | Interrupt Component Configuration       | 5  | 7.7                 | Nested Interrupts                   | 19 |

|   | 3.2  | Interrupt Priority Configuration        | 7  | 8 Sur               | mmary                               | 19 |

|   | 3.3  | Interrupt API Functions                 | 8  | A App               | pendix A – Interrupt Sources and    |    |

| 4 | Wri  | ting an Interrupt Service Routine (ISR) | 10 | Ved                 | ctor Numbers in PSoC 4              | 20 |

|   | 4.1  | Using Auto-Generated ISR                | 11 | Documer             | nt History                          | 22 |

|   | 4.2  | Creating a Custom ISR                   | 12 | Worldwic            | de Sales and Design Support         | 23 |

| 5 | Cod  | de Examples                             | 13 | Products            | )                                   | 23 |

| 6 |      | ougging Tips                            |    | PSoC <sup>®</sup> S | Solutions                           | 23 |

| 7 | Ad۱  | vanced Interrupt Topics                 | 15 |                     |                                     |    |

|   | 7.1  | Exceptions                              | 15 |                     |                                     |    |

#### 1 Introduction

Interrupts are an important part of any embedded application. They free the CPU from having to continuously poll for the occurrence of a specific event; it notifies the CPU only when that event occurs. In system-on-chip (SoC) architectures such as PSoC, interrupts are frequently used to communicate the status of on-chip peripherals to the CPU.

#### Using this document

The document begins with the explanation on PSoC 4 interrupt architecture. If you want to learn about the interrupt support in the PSoC Creator IDE, skip to the Interrupt Support in PSoC Creator. For sample code examples, see Code Examples. If you are debugging the interrupt project, go to the Debugging Tips section, which provides a few tips on finding and resolving interrupt issues. The Advanced Interrupt Topics section covers advanced topics on interrupts.

This application note assumes that you are familiar with PSoC and the PSoC Creator IDE. If you are new to PSoC, you can find an introduction in the *Getting Started with PSoC* application note AN79953 and visit the PSoC Creator home page.

## 2 PSoC 4 Interrupt Architecture

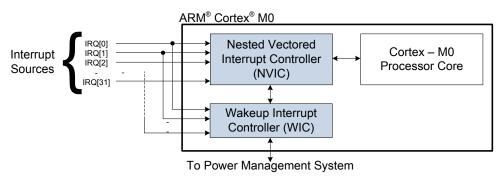

Figure 1 shows a simplified block diagram of the interrupt architecture in PSoC 4:

Figure 1. PSoC 4 Interrupt Architecture

There are 32 interrupt lines – IRQ[0] to IRQ[31] – each with four priority levels, 0 to 3. Each interrupt line is assigned an interrupt vector address. The CPU branches to this address after receiving an interrupt request, where a special function called an Interrupt Service Routine (ISR) is executed.

Interrupt signals are received by the Nested Vectored Interrupt Controller (NVIC). When an interrupt signal becomes active, NVIC sends the interrupt vector address to the processor core along with the interrupt request signal. In return, the processor core sends an acknowledgement when the ISR is entered and exited. The NVIC is responsible for enabling/disabling of any interrupt based on the user configuration. It also resolves the interrupt priority when multiple requests occur at the same time and supports nested interrupts to allow a higher-priority interrupt to be serviced leaving a low-priority ISR.

The Wakeup Interrupt Controller (WIC) block allows the device to wake up from low-power modes – sleep, deep-sleep, and hibernate – using interrupts. The WIC block remains active while the NVIC, processor core, and other device peripherals shut down. When an interrupt triggers, the WIC activates the power management system, which restores the NVIC and the processor core along with other peripherals. The NVIC then takes over and sends the vector address to the processor core to execute the ISR. There are several sources in the PSoC 4 device that has the capability to wake up the device. For example, Figure 1 shows IRQ[0] and IRQ[1] routed to the WIC along with the NVIC. These are the interrupt lines from GPIOs.

PSoC 4 provides the following interrupt features:

- Configurable Interrupt Vector Address: The CPU execution can be directly branched to any ISR code when the interrupt occurs, thus reducing the latency.

- **Flexible Interrupt Sources:** In traditional microcontrollers, the interrupt source is hard-wired to each interrupt line. PSoC gives you the flexibility to choose the interrupt source for each interrupt line. This flexible architecture enables any digital signal to be configured as an interrupt source.

#### 2.1 Interrupt Sources

PSoC 4 interrupt sources are of two types:

- 1. Fixed-function interrupt sources: These are the predefined set of interrupt sources from on-chip peripherals.

- 2. Universal Digital Block (UDB) interrupt sources (available in PSoC 4200, PSoC 42x7\_BLE, PSoC 4200M and PSoC 4200L parts): UDBs are the basic building blocks for different digital functions such as Timer, PWM, UART, SPI, and many more. It consists of programmable logic (PLDs), datapath, and flexible routing. In contrast to fixed-function interrupt sources, any digital signal generated in a UDB can trigger an interrupt. The signals are routed to the interrupt controller through the routing fabric known as Digital System Interconnect (DSI). See the PSoC 4 Technical Reference Manual for more information.

Table 1 shows the interrupt sources. Interrupt sources mentioned in the table are available in all PSoC 4 parts unless noted otherwise. For details on each interrupt source, see the PSoC Creator Component datasheets listed in Table 1. Appendix A shows the complete list of interrupt sources depending on the device.

Table 1. PSoC 4 Interrupt Sources

| Interrupt Source                                       | Details                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GPIOs                                                  | Each port consists of eight pins. Each pin can generate an interrupt, but the vector address common for all pins in a port. Firmware must identify the pin that caused the interrupt.  PSoC 4 enables interrupt trigger on the rising edge, falling edge, or both edges of the GPIO This interrupt can wake the device from sleep, deep-sleep, and hibernate modes. |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Low Power Comparator (LPCOMP) (1)                      | comparato                                                                                                                                                                                                                                                                                                                                                           | Like GPIOs, an interrupt can be triggered on the rising edge, falling edge, or both edges of the comparator output signal. The LPCOMP can also wake the device from sleep, deep-sleep, and hibernate modes.                                                                                                                |  |  |  |  |

| WDT                                                    | has a 16-b                                                                                                                                                                                                                                                                                                                                                          | dog timer (WDT) is a timer that can reset the device or generate an interrupt. PSoC 4000 it free-running WDT, whereas other PSoC 4 parts have two 16-bit WDTs and one 32-bit WDT can wake the device from sleep and deep-sleep modes.                                                                                      |  |  |  |  |

|                                                        | PSoC 4 ha<br>UART.                                                                                                                                                                                                                                                                                                                                                  | s up to four serial communication blocks (SCB), which can be configured as I <sup>2</sup> C, SPI, or                                                                                                                                                                                                                       |  |  |  |  |

| SCB.                                                   | I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                    | The following events generate an interrupt: arbitration lost, slave address match, start/stop detect, bus error, byte/word transfer complete, TX FIFO not full, TX/RX FIFO empty, RX FIFO not empty, RX FIFO overrun, and RX FIFO full. The slave address match event can wake the device from sleep and deep-sleep modes. |  |  |  |  |

| SCB                                                    | SPI                                                                                                                                                                                                                                                                                                                                                                 | The following events generate an interrupt: transfer done, idle, TX FIFO not full, TX/RX FIFO empty, byte/Word transfer complete, RX FIFO is not empty, attempt to write to a full RX FIFO, and RX FIFO full.                                                                                                              |  |  |  |  |

|                                                        | UART                                                                                                                                                                                                                                                                                                                                                                | The following events generate an interrupt: transmission done, UART TX received a NACK in SmartCard mode, UART arbitration lost in LIN or SmartCard mode, frame error, parity error, LIN baud rate detection complete, and LIN successful break detection.                                                                 |  |  |  |  |

| System Performance<br>Controller (SPC)                 | The SPC block controls flash write operations. It triggers an interrupt when the flash write operat complete.                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| SysTick                                                | SysTick is a 24-bit timer built into the ARM® Cortex®-M0 processor. It is generally used by real-time operating systems (RTOS) as a tick timer. However, it can be used as a general-purpose timer. See the SysTick Timer section for more information.                                                                                                             |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Power Manager(1)                                       | This block generates a low-voltage detect (LVD) interrupt when the device supply voltage drops below a threshold.                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| SAR ADC(1)                                             |                                                                                                                                                                                                                                                                                                                                                                     | ssive approximation register analog-to-digital converter (SAR ADC) can generate interrupts conversion, data overflow, scan collision, data saturation, and data over-range events.                                                                                                                                         |  |  |  |  |

| CapSense (CSD)                                         | CSD, used for touch applications, generates an interrupt when the sensor scan is complete.                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Timer, Counter and<br>Pulse Width Modulator<br>(TCPWM) | The TCPWM block can be configured to work as a 16-bit timer, counter, or PWM. It can generate interrupts on terminal count, input capture signal, or a "compare true" event.                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Controller Area Network (CAN)                          | PSoC 4200M and PSoC 4200L devices have two CAN blocks, which can generate interrupts on events such as message received, message sent, and various error events. See the CAN chapter of the Technical Reference Manual for more information.                                                                                                                        |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Direct Memory Access (DMA)                             | PSoC 4100M/4200M and PSoC 4200L have DMA to transfer data between peripherals. An interrupt can be generated when the data transfer is completed.                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Universal Digital Block<br>(UDB)                       | UDB implementations such as timer, PWM, counter, UART, and so on can generate interrupts on different events similar to their fixed-function counterparts. UDBs are available in PSoC 4200, PSoC 42x7_BLE, PSoC 4200M, and PSoC 4200L.                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| USB                                                    | PSoC 4200L has USB with start-of-frame interrupt and interrupt on completion of the communication over data endpoints.                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

<sup>(1)</sup> Not available in PSoC 4000 parts

#### 2.2 Level- and Edge-Triggered Interrupts

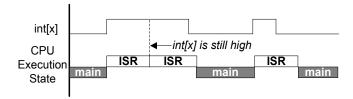

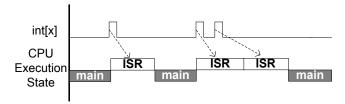

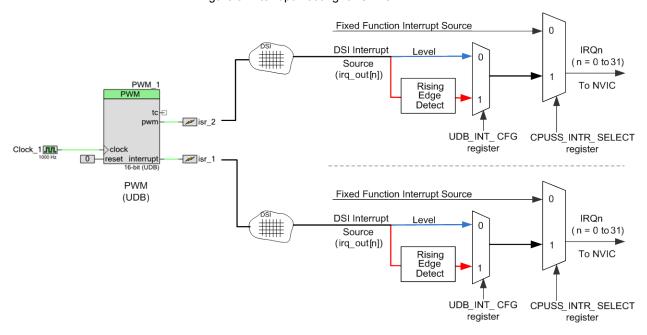

PSoC 4 supports level and edge triggering for interrupts. Figure 2 shows the logic to select the trigger type. This logic is present for each interrupt line supported by NVIC. Note that the fixed-function interrupt can only be configured to level, but for the DSI sources, which include the UDB, the interrupt can be rising-edge triggered as well as leveltriggered. The rising-edge detect block generates a pulse at every rising edge of the DSI interrupt signal. See the timing diagrams (Figure 3 and Figure 4) to know how the NVIC responds to level- and edge-configured interrupts.

Level Fixed Function Interrupt Source **IRQn DSI Interrupt** Level 0 (n = 0 to 31)Source (irq out[n]) Rising To NVIC Edge Detect UDB INT CFG CPUSS INTR SELECT register

Figure 2. Level Trigger and Edge Trigger

Figure 3. Level-Triggered Interrupts

register

Figure 4. Edge-Triggered Interrupts

Note: The GPIO interrupt logic has additional circuitry to support interrupts on the rising edge, falling edge, and both edges. See the PSoC 4 Technical Reference Manual for more information.

## 3 Interrupt Support in PSoC Creator

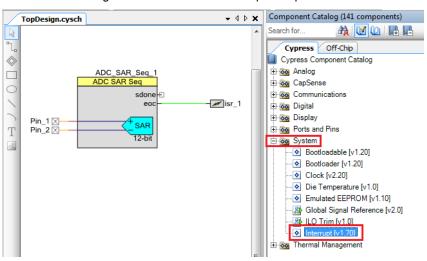

The previous sections show that some properties of interrupts such as the level or edge trigger, vector address, and interrupt priority must be configured. Configuration is facilitated by the PSoC Creator Interrupt Component. This Component is available under the System tab in the Component Catalog window, as Figure 5 shows.

Each instance of the Interrupt Component uses one interrupt line out of the 32 lines that go to NVIC. In the example shown in Figure 5, the end-of-conversion (eoc) signal from the SAR ADC is connected to the Interrupt Component "isr\_1." The SAR ADC has an allotted vector line of the NVIC (see Appendix A). For example, in PSoC 4200, IRQ14 is allotted for SAR ADC interrupt. Thus, the Interrupt Component "isr\_1" wires the eoc signal to the IRQ14 line through the MUX logic shown in Figure 2.

Figure 5. PSoC Creator Interrupt Component

## 3.1 Interrupt Component Configuration

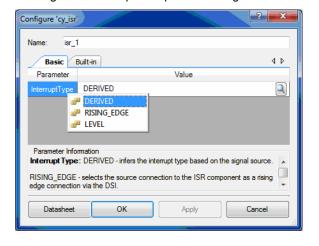

Figure 6 shows the Interrupt Component configuration dialog. There are three options in the Component: DERIVED, RISING EDGE, and LEVEL.

Figure 6. Interrupt Component Configuration

This setting configures the multiplexers shown in Figure 2. The selection of a particular option depends on the interrupt source (fixed-function or UDB/DSI) and the application requirements.

**Fixed-Function Blocks:** The interrupt line from the fixed-function block is always routed through the "dedicated route" as shown by the red line in Figure 7. When configured to this path, the interrupt is level-triggered and the vector number is determined based on the hardware block being used. The Interrupt Component (isr\_1) connected to the interrupt line can only be configured as level-triggered. Setting the interrupt to RISING\_EDGE trigger results in a build error. When configured to DERIVED, the tool selects Level interrupt only.

However, in the PSoC part that has DSI, other output signals from the fixed-function block can be routed for interrupts. This allows the RISING\_EDGE option as shown by the blue line in Figure 7 for the "line" output of a PWM Component. The Interrupt Component (isr\_2) connected to the output of the PWM can be configured to Level or RISING\_EDGE. When the DERIVED option is selected, the tool selects the level trigger configuration. Level trigger in such cases is usually not useful as it causes the ISR to be repeatedly executed as long as signal is HIGH, and so in most cases, RISING\_EDGE is used.

Level Fixed Function Interrupt Source n **IRQn** DSI Interrupt 0 (n = 0 to 31)Source Clock\_1 (irq\_out[n]) Rising To NVIC **TCPWM** Edge (Fixed Function) Detect UDB INT CFG CPUSS\_INTR\_SELECT register register

Figure 7. Interrupt Routing for Fixed-Function Blocks

**UDBs:** For UDBs, the DSI is used to route the signal (from the interrupt line of the UDB Component or any output) to the MUX logic as shown in Figure 8. Thus, both LEVEL and RISING\_EDGE options are available for any signal from the UDB. When the DERIVED option is selected in the Interrupt Component (isr\_1 or isr\_2), the RISING\_EDGE option is configured. This is in contrast to the case of the DSI signal routing for fixed-function block outputs.

Figure 8. Interrupt Routing for UDBs

**Note:** PSoC 4 BLE, PSoC 4 M, and PSoC 4 L parts have 8 DSI channels with each channel demultiplexed to 4 to spread across 32 (8x4) interrupt lines for the ARM Cortex-M0 processor. Thus, the maximum number of DSI interrupts is limited to 8 in a design.

Table 2 provides the guidelines for setting the InterruptType parameter in the Interrupt Component.

Table 2. Interrupt Component Configuration

| Interrupt Source | Signal       | Interrupt Component Configuration                                                                                                    |

|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                  | Interrupt    | Select LEVEL or DERIVED. RISING_EDGE is not allowed.                                                                                 |

| Fixed-Function   | Block output | Select RISING_EDGE; otherwise, the interrupt will be repeatedly triggered for the duration of the logic HIGH signal state.           |

|                  | Interrupt    | Select RISING_EDGE or DERIVED.                                                                                                       |

| UDB Function     | Block output | Select RISING_EDGE; selecting LEVEL causes the interrupt to be repeatedly triggered for the duration of the logic HIGH signal state. |

#### 3.1.1 Sticky Bits

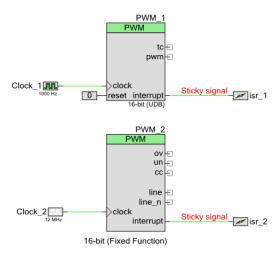

An interrupt signal may be "sticky", which means that the interrupt line remains active (HIGH) until it is read or cleared. In this case, if the Interrupt Component is configured to RISING\_EDGE, the ISR is executed once. If the Interrupt Component is configured to LEVEL, the ISR is executed repeatedly. To handle this, clear the interrupt source by using the API provided by the Component. See the Component datasheet of the interrupt source. You can also refer the Writing an Interrupt Service Routine (ISR) section, which provides an example using the timer interrupt.

Note that when the output lines of a fixed-function block or the UDB (for example, "pwm" line of a PWM Component as shown in Figure 9) are connected to the Interrupt Component instead of the interrupt line, there is no need to clear the interrupt. However, the ISR is repeatedly executed as long as the signal is HIGH, if the interrupt Component is configured to LEVEL.

Figure 9. Sticky Signal

#### 3.2 Interrupt Priority Configuration

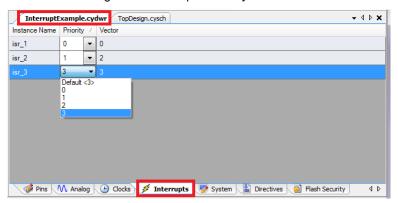

The design-wide resources window (*project\_name.cydwr*) of the PSoC Creator project has an Interrupts tab, which displays the Interrupt Component instance names, their priorities, and vector numbers, as Figure 10 shows. isr\_1, isr\_2, and isr\_3 are the Interrupt Components used in the design.

Figure 10. Interrupt Tab in cydwr Window

Use the *cydwr* window to change the priority of an interrupt. Remember that 0 is the highest priority; and 3, the lowest priority. The Cortex-M0 supports interrupt nesting; see Nested Interrupts for details.

The interrupt vector number for each Interrupt Component is automatically assigned by PSoC Creator when the project is built, but can be manually changed. See Forcing the Interrupt Vector Number for details. Also, note that the vector number is shown with an offset in the .cydwr window. Vector number of 0 corresponds to exception number 16 in Cortex-M0. See Exceptions for an overview of Cortex-M0 exceptions.

#### 3.3 Interrupt API Functions

PSoC Creator generates an API –.c and .h files – for each Component in the project. These APIs include functions to configure and use each Component. The following API functions are associated with an Interrupt Component:

- <instance name> StartEx()

Similar to Start(); the only difference is that this function takes a vector address as an input, enabling you to write a custom ISR rather than using the default ISR generated by the Component.

■ <instance name> Enable()and <instance name>\_Disable()

These functions are called internally by Start() and Stop() to enable and disable the interrupt. These functions can be called to dynamically enable and disable an interrupt.

<instance name> SetVector() and <instance name> SetPriority()

These functions are called internally by <code>Start()</code> and <code>Stop()</code> to set the interrupt vector address and the interrupt priority. These functions can also be called to dynamically set the vector and the priority. Make sure that the interrupt is disabled before calling these functions.

■ <instance name> SetPending()

Makes the interrupt pending without an interrupt request, i.e., under firmware control.

<instance name> ClearPending()

Clears the pending status of the interrupt so that it is not serviced. This function does not have any effect on the interrupt source signal; it only clears the pending status bit of the interrupt line in the NVIC.

See the Interrupt Component Datasheet for a detailed explanation of the API.

#### 3.3.1 Critical Section Control Functions

PSoC Creator also provides a set of generic interrupt functions in the *CyLib.h* and *CyLib.c* files. These files are generated when the project is built. The important ones are <code>CyEnterCriticalSection</code> and <code>CyExitCriticalSection</code>. These two functions are used to avoid the corruption of firmware variables and hardware registers. <code>CyEnterCriticalSection</code> disables interrupts and returns an interrupt state value. <code>CyExitCriticalSection</code> restores the interrupt state.

To see how this works, consider an example of writing to a timer control register:

```

TCPWM BLOCK CONTROL REG |= TCPWM MASK;

```

The following sequence of operations occurs while executing the statement above:

- The CPU reads the control register of the TCPWM and stores it in a temporary register.

- 2. The CPU executes a logical OR operation of the temporary register with its mask value.

- 3. The CPU loads the OR result back to the control register.

Between steps 1 and 2, an interrupt may occur, and its ISR may load a new value into the same control register. After executing the ISR, when the CPU resumes executing step 2, it uses the stale control register value, which was in the temporary register—this leads to data corruption.

To avoid this issue, add the following code:

```

InterruptState = CyEnterCriticalSection();

TCPWM_BLOCK_CONTROL_REG |= TCPWM_MASK;

CyExitCriticalSection(InterruptState);

```

The CyEnterCriticalSection and CyExitCriticalSection functions solve the problem by disabling interrupts while the control register is being written. Use these functions when a shared variable or register is being written.

For details on these functions, see the System Reference Guide (also available under the PSoC Creator menu **Help > Documentation**).

## 4 Writing an Interrupt Service Routine (ISR)

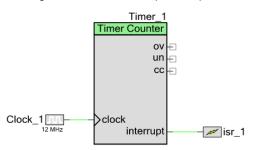

To understand how to write an ISR, consider a timer interrupt as an example. The Interrupt Component "isr\_1" is connected to the interrupt terminal of Timer\_1, as Figure 11 shows.

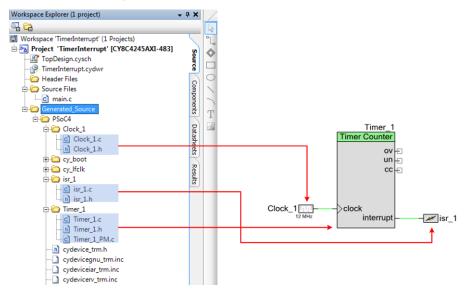

After building the project, PSoC Creator generates the files associated with all the Components as shown in Figure 12. *isr\_1.c* and *isr\_1.h* are the files generated for the Interrupt Component isr\_1. These files provide the API for configuring and using the Component, including the ISR.

Figure 11. Timer Interrupt Example

Figure 12. Files Generated for Interrupt Components

There are two ways to write an ISR - using the PSoC Creator auto-generated ISR and creating a custom ISR function.

#### 4.1 Using Auto-Generated ISR

The following is an ISR generated by default in  $isr\_1.c$ . The ISR function name is in the format - CY\_ISR( $<isr\_name>\_interrupt$ ).

```

CY_ISR(isr_1_Interrupt)

{

/* Place your Interrupt code here. */

/* `#START isr_1_Interrupt` */

/* `#END` */

}

```

You can write the code in this auto-generated ISR between the #START and #END markers. Note that code written outside these markers is deleted when the project files are re-generated.

To enable the interrupt, start the isr Component. The following is the *main.c* code to start the interrupt source, that is, the timer and the Interrupt Component.

```

int main()

{

/* Start the timer component */

Timer_1_Start();

/* Start the interrupt component */

isr_1_Start();

/* Enable global interrupt */

CyGlobalIntEnable;

for(;;)

{

/* Place your application code here. */

}

}

```

Note that in addition to enabling the Interrupt Component, you must enable the global interrupt using the CyGlobalIntEnable macro. Inside the ISR, clear the interrupt as explained in Sticky Bits. In this example, the Timer interrupt is cleared using the following API function:

```

void Timer_1_ClearInterrupt(uint32 interruptMask)

```

The interruptMask parameter can be the Timer Component's terminal count interrupt mask or compare/capture count interrupt mask – see the Timer Component datasheet or the *timer\_1.h* file. See other Component datasheets to know about the API and the interrupt mask that clears the interrupt from a particular Component.

#### 4.2 Creating a Custom ISR

The ISR can be written in your own source file instead of inside the auto-generated code. To make your own function, for example MyCustomISR, to be the ISR for an Interrupt Component isr\_1, do the following:

1. Declare the custom function using the CY ISR PROTO macro:

```

CY ISR PROTO (MyCustomISR);

```

2. Define the custom function using the CY ISR macro:

```

CY_ISR(MyCustomISR)

{

/* ISR code goes here */

}

```

3. In the startup code of your *main.c* file, add a call to the API function <code>isr\_1\_StartEx()</code> instead of <code>isr\_1\_Start()</code>. The <code>isr\_1\_StartEx()</code> API function is similar to the <code>isr\_1\_Start()</code> API function except that <code>isr 1 StartEx()</code> has a parameter for your ISR function: <code>isr 1 StartEx(MyCustomISR);</code>

#### 4.2.1 Significance of the Keyword CY\_ISR

The interrupt source file defines the ISR function using the  $CY_{ISR}$  macro. This macro is defined in the autogenerated *cytypes.h* file. It is used for compatibility and easy code porting to other PSoC device families such as PSoC 3 or PSoC 5LP.

Similarly, the macro CY\_ISR\_PROTO declares an ISR function prototype. The declaration is in the header file of the Interrupt Component. For example, the Interrupt Component  $isr_1$  has the following function prototype declaration in the header file  $isr_1$ .

```

CY ISR PROTO(isr 1 Interrupt);

```

## 5 Code Examples

Table 3 provides the list of code examples that uses interrupt feature.

Table 3. Interrupt Code Examples

| Code Example                                                            | Interrupt Source |

|-------------------------------------------------------------------------|------------------|

| CE210557 – PSoC 4 Timer Interrupt                                       | Timer            |

| CE210558 – PSoC 4 GPIO Interrupt                                        | GPIO             |

| CE95915 – Implementing an RTC with PSoC® 4100/PSoC 4200 Devices         | TCPWM            |

| CE95333 – Low Power Comparator with PSoC 4                              | LPCOMP           |

| CE95321 – Hibernate and Stop Power Modes with PSoC 4                    | LPCOMP, GPIO     |

| CE95400 – Watchdog Timer Reset and Interrupt for PSoC 41xx/42xx Devices | WDT              |

| CE95275 – Sequencing SAR ADC and Die temperature sensor with PSoC 4     | SAR ADC          |

| CE95298 – Switch Debouncer with PSoC 3/4/5LP                            | GPIO, Debouncer  |

| CE97089 – PSoC 4 ADC to Memory Buffer DMA Transfer                      | DMA              |

## 6 Debugging Tips

This section provides tips on debugging the interrupt projects. The following are some of the frequently encountered cases:

#### a. Interrupt is not getting triggered

- Ensure that the interrupt source and global interrupt is enabled.

- Check if the vector is set to the correct ISR. See Writing an Interrupt Service Routine (ISR) for more

details on how to write and assign the handler for an interrupt source.

- Check if there are other interrupt sources that are getting repeatedly triggered, thus consuming the entire CPU bandwidth.

- Check if the interrupt is getting triggered only once. This happens if the Interrupt Component is configured to rising edge and the interrupt source is not cleared.

#### b. Interrupt is triggered repeatedly

This can happen in multiple cases:

- The interrupt line from the source Component is connected to the Interrupt Component configured to level type. Clear the interrupt source to resolve this behavior.

- A digital output from the Component (not the interrupt line) is connected to the Interrupt Component configured to level type. Configure the Interrupt Component to rising edge to get one interrupt per rising edge.

See Sticky Bits for more details.

#### c. Interrupt is triggered only once

The interrupt line from the source Component is connected to the Interrupt Component configured to rising edge type. Clear the interrupt source to allow interrupt to be triggered for every rising edge. See Sticky Bits for more details.

#### d. Execution of the Interrupt service routine (ISR) is taking longer time than expected

This can happen if other high priority interrupts are being triggered during the execution of the ISR. Increase the priority of the interrupt relative to other interrupt sources.

PSoC 4 devices have on-chip debug capability using the Serial Wire debug (SWD) interface. It allows you to add breakpoints, evaluate and edit variables, view CPU registers, observe assembler instructions, and read and write memory.

The debug mode is useful for checking interrupts as given below:

- To check if the interrupts are getting executed, add a breakpoint in one of the instructions of the ISR.

- Use the Call Stack window of the debugger to check at what moment a particular interrupt is getting executed. You can also use it to check if a high-priority interrupt occurred during the execution of a low-priority ISR.

Use Breakpoint Hit Count to detect the number of times an interrupt is being triggered. This is particularly useful to check if the interrupt signal has glitches causing the interrupt to trigger multiple times.

For more details on how to use the Debugger, see the "Using the Debugger" section in PSoC Creator Help. To access the document, press F1 or use Help > Topics menu in PSoC Creator.

As an alternative to debugger, you can also bit bang a pin to do the following:

- Check if the CPU is entering the ISR.

- Measure the ISR execution time. This can be done by setting the pin in the beginning of the ISR and resetting the pin at the end.

## 7 Advanced Interrupt Topics

### 7.1 Exceptions

Exceptions are the events that cause the processor to suspend the currently executing code and branch to a handler. Interrupts are a subset of exceptions. Besides interrupts, exceptions exist for operating system applications and fault handling, as Table 4 shows.

Exception Exception Interrupt Description Number Priority Reset 1 -3 (Highest) This exception is triggered on power-on-reset or external reset. It is the exception generated on fault conditions such as the detection 3 Hard Fault of undefined opcode. It is triggered on a supervisory call (execution of the SVC instruction). SVCall (Supervisor call) Programmable It is normally used in operating system applications. This is similar to SVCall, but the branching to the handler is done PendSV (Pendable Programmable 14 only after all high priority tasks are completed. service call) SysTick is a 24-bit down-counting timer present in Cortex M0. It Programmable generates periodic interrupts for use in operating system SysTick 15 applications. IRQ0 to IRQ31 16 - 47Programmable External (Pins) or internal peripheral interrupts Reset -3 (Highest) This exception is triggered on power-on-reset or external reset.

Table 4. Exceptions in ARM Cortex M0

Note that the exception numbers are defined by ARM. The interrupt vector numbers, shown in the **Interrupt** tab of the *.cydwr* window in the PSoC Creator project, include an exception offset. For example, interrupt vector 0 is exception number 16 (IRQ0).

Reset is the highest-priority exception in the device followed by Hard Fault. These have a fixed priority, whereas others have programmable priorities. PSoC Creator provides a default handler for all exceptions. For reset, the default handler is Reset() in the *Cm0Start.c* file. This function is executed first on startup. For all other exceptions, the IntDefaultHandler() function is the default handler provided in the *Cm0Start.c* file. However, vector addresses of the used exceptions including interrupts (defined by the PSoC Creator Components or by the user) are loaded into the vector table during program execution. Unused exceptions still use the default handler.

To identify which exception is currently being handled, read the Interrupt Program Status Register (IPSR). This is particularly useful when the default handler is under execution.

For more details on exceptions, see http://infocenter.arm.com/help/index.jsp.

### 7.2 Interrupt Latency

Interrupt latency is defined as the time delay between the assertion of an interrupt and the execution of the first instruction in its ISR. The ARM Cortex-M0 processor in the PSoC 4 device has a latency of 16 CPU clock cycles (worst-case) with additional CPU cycles because of synchronizer between peripherals and the Cortex-M0 interrupt lines. Table 5 provides the synchronizer CPU clock cycle delays in different PSoC 4 families for DSI and fixed-function source interrupts.

Table 5. Synchronizer Clock Cycle Delays for DSI and Fixed-Function Source Interrupts

| Device DSI Interrupt          |              | Fixed-Function Interrupt           |  |  |  |

|-------------------------------|--------------|------------------------------------|--|--|--|

|                               |              | Depends on the peripheral:         |  |  |  |

| PSoC 4000                     | NA           | ■ SCB-I2C, GPIO, WDT: 3 CPU cycles |  |  |  |

|                               |              | ■ SPC, CSD, TCPWM: 0 CPU Cycles    |  |  |  |

| PSoC 4200 / PSoC 4100         | 0 CPU cycles | 3 CPU Cycles                       |  |  |  |

| PSoC 42x7 BLE / PSoC 41x7 BLE | 3 CPU cycles | Depends on the peripheral:         |  |  |  |

| Device                    | DSI Interrupt   | Fixed-Function Interrupt                                                                                 |  |  |

|---------------------------|-----------------|----------------------------------------------------------------------------------------------------------|--|--|

|                           |                 | ■ SCB-I2C, GPIO, WDT, CTBm, LPCOMP, BLE, LVD: 3 CPU cycles                                               |  |  |

|                           |                 | ■ SPC, CSD, TCPWM, SAR: 0 CPU cycles                                                                     |  |  |

|                           |                 | Depends on the peripheral:                                                                               |  |  |

| PSoC 4200M / PSoC 4100M / | 3 CPU cycles    | ■ SCB-I2C, GPIO, WDT, CTBm, LPCOMP, LVD: 3 CPU cycles                                                    |  |  |

| PSoC 4200L                | 5 OF 0 Cycles ■ | <ul> <li>SPC, CSD, TCPWM, SAR, DMA, CAN, USB (only available in PSoC<br/>4200L): 0 CPU cycles</li> </ul> |  |  |

During the 16-cycles latency in Cortex M0, the following actions take place:

- 1. The processor pushes the current Program Counter (PC), Link Register (LR), Program Status Register (PSR), and some of the general-purpose registers to the stack.

- 2. The processor reads the vector address from the NVIC and updates it to the PC.

- 3. The processor updates the NVIC registers.

Thus, the latency differs from 16 cycles when an ISR is currently in execution or about to begin. To make the process efficient, the Cortex-M0 processor implements the following two schemes:

- Tail Chaining: If an interrupt is in the pending state while the processor is executing another interrupt handler, unstacking is skipped when the execution ends for the first interrupt and the handler for the pending interrupt is immediately executed. This saves the time of restoring the registers from the stack and pushing the same registers again to stack. This is useful for reducing the latency of low-priority interrupts.

- 2. Late Arrival: If a higher-priority interrupt occurs during the stacking process of a lower-priority interrupt, the processor jumps to the higher-priority interrupt handler instead of a lower-priority one. The processor reads the vector address of the higher-priority interrupt at the end of the stacking process. Once the higher-priority interrupt handler execution is completed, the vector address for the pending lower-priority interrupt handler is fetched and executed. This reduces the latency for a higher-priority interrupt by eliminating the delay caused by entering the lower-priority ISR and pushing the register values to the stack.

Note that the current instruction in execution when the interrupt is triggered causes an additional delay in the execution of the ISR. In the case of a device wake-up from an interrupt, an additional delay is caused by the voltage stabilization after the power-up sequence. See the device datasheet for specifications.

#### 7.3 Optimizing the Interrupt Code

One of the important performance requirements in interrupt-based applications is the ISR code execution time. In some applications, the critical code in the ISR must be executed within a particular time of receiving the interrupt request. Also, interrupt execution should not take too much time and stall the main code execution or other interrupts. To meet these requirements, use the following guidelines:

- Avoid calls to the lengthy functions in the ISR. Functions such as Character LCD display routines takes long time to execute thus blocking the execution of other low-priority interrupts.

- The recommended technique is to move noncritical function calls to the main code and just set a flag variable in the ISR. The main code periodically checks the flag and if set, clears it and calls the function.

- Assign proper priority to the interrupts. In applications with multiple interrupts, give a higher priority to more time-critical interrupts.

#### 7.4 Components with Inbuilt Interrupts

Many PSoC Creator Components have an Interrupt Component internally as part of their implementation. Examples include CapSense, SAR ADC, EZI2C, and Segment LCD.

Similar to Interrupt Components, internal ISRs in these Components provide a placeholder region for writing user code. See the respective Component datasheets and associated code examples provided in PSoC Creator to understand the interrupt usage in these Components.

#### 7.5 Forcing the Interrupt Vector Number

PSoC Creator automatically assigns the vector numbers for the Interrupt Components in a project. After building the project, you can view the assigned vector numbers in the Interrupts tab of the *.cydwr* window, as Figure 13 shows. You can also select a particular vector number for an interrupt signal when it is routed through the DSI. This section provides a step-by-step procedure to do this.

Figure 13. Interrupt Vector Numbers in cydwr Window

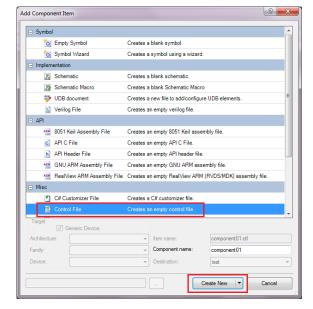

To override the vector numbers assigned by PSoC Creator and manually assign a vector number, a *Control File* is used. Follow the steps given below:

- 1. Click the **Components** tab of the Workspace Explorer window.

- Right-click the TopDesign Component and select Add Component Item.... The Add Component Item dialog opens.

- 3. Scroll down to the Misc group, select Control File, and click Create New, as Figure 14 shows.

Figure 14. Adding the Control File

A *TopDesign.ctl* file is created and added to the Workspace Explorer window.

- 4. Double-click the *TopDesign.ctl* file to open it for editing. The *attribute* keyword is used in the control file to specify the interrupt vector number for each Interrupt Component. The method of specifying the interrupt vector number depends on whether the Interrupt Component has been placed by the user on the example schematic or the Interrupt Component is used internally in a PSoC Creator Component in the schematic. The two methods are as follows:

- a) For the Interrupt Components placed by the user on the schematic, the syntax is:

attribute placement\_force of instance\_name : label is "Intr(0, DesiredVectorNumber)";

Here, <code>instance\_name</code> refers to the name of the Interrupt Component in the schematic and <code>DesiredVectorNumber</code> is the vector number (0 to 31). For example, to assign vector 17 to the Interrupt Component <code>isr\_1</code>:

```

attribute placement_force of isr_1 : label is "Intr(0, 17)";

```

b) For Components that use interrupts internally such as EZI2C, the syntax is:

```

attribute placement_force of \top_instance_name : InternalInterruptName\: label is

"Intr(0, DesiredVectorNumber)";

```

Here, top\_instance\_name refers to the name of the Component that uses the interrupt internally. InternalInterruptName refers to the name assigned for the internal interrupt in the Component. This can be found from the Interrupts tab of the *cydwr* window, where the interrupt name is appended to the top Component instance name. In Figure 13, SCB\_IRQ is the internal interrupt name for the EZI2C Component and the UART Component. The following statement assigns the vector for EZI2C Component to 11.

```

attribute placement_force of \EZI2C_1:SCB_IRQ\ : label is "Intr(0,11)"

```

After assigning the interrupt vector numbers, click Save to save the changes made to the control file.

5. **Clean and Build** the example for the new interrupt vector assignments to take effect. The Interrupts tab in the *cydwr* window now shows the modified interrupt vector number assignments.

#### 7.6 SysTick Timer

SysTick is a 24-bit down-counting timer. Its interrupt is generally used for task switching in a real-time system. It uses the Cortex-M0 internal clock for counting. SysTick is configured using the APIs given below:

1. Setting interrupt handler

```

CyIntSetSysVector(SYSTICK_VECTOR_NUMBER, SysTick_ISR);

```

SYSTICK\_VECTOR\_NUMBER is the exception number for the SysTick interrupt, which is 15 for Cortex-M0. SysTick\_ISR is the interrupt handler.

2. Configuring interrupt period

```

(void) SysTick_Config(CLOCK_FREQ / INTERRUPT_FREQ);

```

CLOCK\_FREQ is the CPU clock frequency. INTERRUPT\_FREQ is the derived interrupt rate from SysTick. Below is the code snippet for SysTick timer usage:

```

CY_ISR(SysTick_ISR)

{

/* Interrupt Handler */

}

```

### 7.7 Nested Interrupts

NVIC automatically handles the nested interrupts without any software overhead. If a higher-priority interrupt is asserted during the execution of a lower-priority interrupt handler, some of the general-purpose registers are pushed to stack, processor core reads the vector address from NVIC and jumps to the higher-priority interrupt handler. After the execution is completed, the processor restores the register values and execution resumes for the lower-priority interrupt.

## 8 Summary

Interrupts are commonly used in embedded applications. For system-on-chip architectures such as PSoC 4, interrupts play the critical role of communicating the status of on-chip peripherals to the CPU. This application note has provided the information needed to understand the infrastructure available and create interrupt based projects.

#### **About the Author**

Name: Rajiv Badiger

Title: Applications Engineer Staff

Background BE Electronics and Communication

## A Appendix A – Interrupt Sources and Vector Numbers in PSoC 4

Table 6 lists the interrupt sources for the 32 interrupt vectors in PSoC 4.

Table 6. PSoC 4 Interrupt Sources ('-' Indicates function not available)

|                                           | DSI Interrupt Source<br>(not for PSoC 4000) | Interrupt Vector |                   |            |          |          |  |

|-------------------------------------------|---------------------------------------------|------------------|-------------------|------------|----------|----------|--|

| Fixed Function Interrupt<br>Source        |                                             | PSoC<br>4000     | PSoC<br>4100/4200 | PSoC 4 BLE | PSoC 4 M | PSoC 4 L |  |

|                                           |                                             |                  |                   |            |          |          |  |

| GPIO Interrupt – Port 0                   | DSI                                         | IRQ0             | IRQ0              | IRQ0       | IRQ0     | IRQ0     |  |

| GPIO Interrupt – Port 1                   | DSI                                         | IRQ1             | IRQ1              | IRQ1       | IRQ1     | IRQ1     |  |

| GPIO Interrupt – Port 2                   | DSI                                         | IRQ2             | IRQ2              | IRQ2       | IRQ2     | IRQ2     |  |

| GPIO Interrupt – Port 3                   | DSI                                         | IRQ3             | IRQ3              | IRQ3       | IRQ3     | IRQ3     |  |

| GPIO Interrupt – Port 4                   | DSI                                         |                  | IRQ4              | IRQ4       | IRQ4     | IRQ4     |  |

| GPIO Interrupt – Port 5                   | DSI                                         | _                | _                 | IRQ5       | _        | _        |  |

| GPIO Interrupt – Port 13<br>(USB Wake up) | DSI                                         | _                |                   | _          | _        | IRQ5     |  |

| GPIO Interrupt – All Port*                | DSI                                         | _                | _                 | IRQ6       | IRQ5     | IRQ6     |  |

| _                                         | DSI                                         | _                | IRQ5              | _          | _        | _        |  |

| _                                         | DSI                                         | _                | IRQ6              | _          | _        | _        |  |

| _                                         | DSI                                         | _                | IRQ7              | _          | _        | _        |  |

| LPCOMP (low-power comparator)             | DSI                                         | _                | IRQ8              | IRQ7       | IRQ6     | IRQ7     |  |

| WDT (Watchdog timer)                      | DSI                                         | IRQ4             | IRQ9              | IRQ8       | IRQ7     | IRQ8     |  |

| SCB0 (Serial<br>Communication Block 0)    | DSI                                         | IRQ5             | IRQ10             | IRQ9       | IRQ8     | IRQ9     |  |

| SCB1 (Serial<br>Communication Block 1)    | DSI                                         | _                | IRQ11             | IRQ10      | IRQ9     | IRQ10    |  |

| SCB2 (Serial<br>Communication Block 2)    | DSI                                         | _                | _                 | _          | IRQ10    | IRQ11    |  |

| SCB3 (Serial<br>Communication Block 3)    | DSI                                         | _                | _                 | _          | IRQ11    | IRQ12    |  |

| CTBm Interrupt (all CTBms)                | DSI                                         | _                |                   | IRQ11      | IRQ12    | IRQ13    |  |

| BLE Subsystem Interrupt                   | DSI                                         | _                |                   | IRQ12      | _        | _        |  |

| DMA Interrupt                             | DSI                                         |                  | _                 | _          | IRQ13    | IRQ14    |  |

| SPCIF Interrupt DSI                       |                                             | IRQ6             | IRQ12             | IRQ13      | IRQ14    | IRQ15    |  |

| SRSS LVD Interrupt DSI                    |                                             | _                | IRQ13             | IRQ14      | IRQ15    | IRQ16    |  |

| SAR (Successive DSI Approximation ADC)    |                                             | _                | IRQ14             | IRQ15      | IRQ16    | IRQ17    |  |

| CSD0 (CapSense)                           | DSI                                         | IRQ7             | IRQ15             | IRQ16      | IRQ17    | IRQ18    |  |

| CSD1 (CapSense)                           | DSI                                         | _                | _                 | _          | IRQ18    | IRQ19    |  |

|                                    | DSI Interrupt Source | Interrupt Vector |                   |            |          |          |

|------------------------------------|----------------------|------------------|-------------------|------------|----------|----------|

| Fixed Function Interrupt<br>Source | (not for PSoC 4000)  | PSoC<br>4000     | PSoC<br>4100/4200 | PSoC 4 BLE | PSoC 4 M | PSoC 4 L |

| TCPWM0<br>(Timer/Counter/PWM 0)    | DSI                  | IRQ8             | IRQ16             | IRQ17      | IRQ19    | IRQ20    |

| TCPWM1<br>(Timer/Counter/PWM 1)    | DSI                  | _                | IRQ17             | IRQ18      | IRQ20    | IRQ21    |

| TCPWM2<br>(Timer/Counter/PWM 2)    | DSI                  | _                | IRQ18             | IRQ19      | IRQ21    | IRQ22    |

| TCPWM3<br>(Timer/Counter/PWM 3)    | DSI                  | _                | IRQ19             | IRQ20      | IRQ22    | IRQ23    |

| TCPWM4<br>(Timer/Counter/PWM 4)    | DSI                  | _                | _                 | _          | IRQ23    | IRQ24    |

| TCPWM5<br>(Timer/Counter/PWM 5)    | DSI                  | _                | _                 | _          | IRQ24    | IRQ25    |

| TCPWM6<br>(Timer/Counter/PWM 6)    | DSI                  | _                | _                 | _          | IRQ25    | IRQ26    |

| TCPWM7<br>(Timer/Counter/PWM 7)    | DSI                  | _                | _                 | _          | IRQ26    | IRQ27    |

| CAN0 Interrupt                     | DSI                  | _                | _                 | _          | IRQ27    | IRQ28    |

| CAN1 Interrupt                     | DSI                  |                  | _                 | _          | IRQ28    | IRQ29    |

| USB Start of Frame                 | DSI                  | _                | _                 | _          | _        | IRQ30    |

| USB EP1-EP8 Data                   | DSI                  | _                | _                 | _          | _        | IRQ31    |

| _                                  | DSI                  | _                | IRQ20             | IRQ21      | IRQ29    | _        |

| _                                  | DSI                  | _                | IRQ21             | IRQ22      | IRQ30    | _        |

| _                                  | DSI                  | _                | IRQ22             | IRQ23      | IRQ31    | _        |

| _                                  | DSI                  |                  | IRQ23             | IRQ24      | _        | _        |

| _                                  | DSI                  |                  | IRQ24             | IRQ25      | _        | _        |

| _                                  | DSI                  | _                | IRQ25             | IRQ26      | _        | _        |

| _                                  | DSI                  |                  | IRQ26             | IRQ27      | _        | _        |

| _                                  | DSI                  | _                | IRQ27             | IRQ28      | _        | _        |

| _                                  | DSI                  |                  | IRQ28             | IRQ29      | _        | _        |

| _                                  | DSI                  |                  | IRQ29             | IRQ30      | _        | _        |

| _                                  | DSI                  | _                | IRQ30             | IRQ31      | _        | _        |

| _                                  | DSI                  | _                | IRQ31             | _          | _        | _        |

# **Document History**

Document Title: AN90799 – PSoC® 4 Interrupts

Document Number: 001-90799

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                         |  |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| **       | 4371470 | RJVB               | 05/22/2014         | New Application Note                                                                                                                                                                                                                                                                                                                          |  |

| *A       | 4765616 | RJVB               | 05/14/2015         | Updated for PSoC 4 BLE and PSoC 4 M Added section on Writing Interrupt Handlers Added details on interrupts latency Provided links for PSoC Creator code examples Updated projects with PSoC Creator 3.2 Updated Appendix B with development kits Added information on CyEnterCriticalSection and CyExitCriticalSection APIs Updated template |  |

| *B       | 4968362 | RJVB               | 02/02/2016         | Updated for PSoC 4200L.  Added Exceptions and Debugging Tips.  Updated Introduction, PSoC 4 Interrupt Architecture and Interrupt Priority Configuration.  Removed projects from the application note and moved to code examples CE210557 and CE210558.                                                                                        |  |

## **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive cypress.com/go/automotive

Clocks & Buffers cypress.com/go/clocks

Interface cypress.com/go/interface

Lighting & Power Control cypress.com/go/powerpsoc

Memory cypress.com/go/memory

PSoC cypress.com/go/psoc

Touch Sensing cypress.com/go/touch

USB Controllers cypress.com/go/usb

Wireless/RF cypress.com/go/wireless

## PSoC® Solutions

psoc.cypress.com/solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

## **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

## **Technical Support**

cypress.com/go/support

PSoC is a registered trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone : 408-943-2600 Fax : 408-943-4730 Website : www.cypress.com

© Cypress Semiconductor Corporation, 2014-2016. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. Use may be limited by and subject to the applicable Cypress software license agreement.