## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

### **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

## Cypress EZ-PD™ CCGx Host SDK User Guide

Revision 3.4.0

Doc. No. 002-24327 Rev. \*D

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone (USA): 800.858.1810 Phone (Intl): 408.943.2600

www.cypress.com

© Cypress Semiconductor Corporation, 2018-2020. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

| 1.   | Introduction                                     | 5  |

|------|--------------------------------------------------|----|

| 1.1  | USB Type-C and Power Delivery                    | 5  |

| 1.2  | EZ-PD™ Type-C Controllers                        | 5  |

| 1.3  | CCGx Host SDK                                    | 5  |

| 2.   | SDK Installation                                 | 10 |

| 2.1  | SDK Installation                                 | 10 |

| 2.2  | Tool Dependencies                                | 10 |

| 2.3  | Hardware Dependencies                            | 11 |

| 3.   | Getting Started with CCGx Host SDK               | 12 |

| 3.1  | Preparing to use PSoC Creator                    | 12 |

| 3.2  | Using the Reference Projects                     | 13 |

| 3.3  | Updating CCGx Configuration                      | 23 |

| 4.   | Customizing the Firmware Application             | 33 |

| 4.1  | Solution Structure                               | 33 |

| 4.2  | Compile Time Options                             | 34 |

| 4.3  | Part Number Update                               | 39 |

| 4.4  | USB-PD Specification Revision Support            | 41 |

| 4.5  | CYPD6227-96BZXI_notebook_tbt Application         | 42 |

| 4.6  | CYPD6227-96BZXI_notebook_dualapp_tbt Application | 49 |

| 4.7  | CYPD6227-96BZXI_notebook_dualapp Application     | 50 |

| 4.8  | CYPD6125-40LQXI_notebook Application             | 55 |

| 4.9  | CYPD5126-40LQXI_notebook Application             | 61 |

| 4.10 | CYPD5125-40LQXI_notebook Application             | 67 |

| 4.11 | CYPD5225-96BZXI_notebook Application             | 73 |

| 4.12 | CYPD4126-24LQXI_notebook application             | 75 |

| 4.13 | CYPD4126-40LQXI_notebook application             | 80 |

|      |                                                  |    |

| 4.14 | CYPD4226-40LQXI_notebook application | 81  |

|------|--------------------------------------|-----|

| 4.15 | CYPD3125-40LQXI_notebook application | 84  |

| 4.16 | CYPD3126-42FNXI_notebook application | 88  |

| 5.   | Firmware Architecture                | 89  |

| 5.1  | Firmware Blocks                      | 89  |

| 5.2  | SDK Usage Model                      | 90  |

| 5.3  | Firmware Versioning                  | 91  |

| 5.4  | Flash Memory Map                     | 93  |

| 5.5  | Bootloader                           | 94  |

| 5.6  | Firmware Operation                   | 96  |

| 6.   | Firmware APIs                        | 99  |

| 6.1  | Data Structures                      | 99  |

| 6.2  | API Summary                          | 100 |

| 6.3  | API Usage Examples                   | 113 |

| 7.   | Revision History                     | 129 |

| 7.1  | Document Revision History            |     |

## 1. Introduction

### 1.1 USB Type-C and Power Delivery

USB Type-C is the new USB-IF standard that solves several challenges faced by today's Type-A and Type-B cables and connectors. USB Type-C uses a slimmer connector (measuring only 2.4 mm in height) to enable increasing miniaturization of consumer and industrial products. The USB Type-C standard is gaining rapid support by enabling small form-factor, easy-to-use connectors, and cables that can transmit multiple protocols. In addition, it offers power delivery up to 100 W – a significant improvement over the 7.5 W for previous standards.

### 1.1.1 USB Type-C Highlights

- New reversible connector measuring only 2.4 mm in height.

- Compliant with USB Power Delivery Specification, providing up to 100 W.

- Increases the data bandwidth to 40 Gbps with USB4™.

- Combines multiple protocols in a single cable, including DisplayPort™, PCle<sup>®</sup>, and Thunderbolt™.

## 1.2 EZ-PD™ Type-C Controllers

Cypress offers the EZ-PD line of Type-C controllers, which currently include six product families:

- EZ-PD™ CCG1: Industry's First Programmable Type-C Port Controller

- EZ-PD™ CCG2: Industry's Smallest Programmable Type-C Port Controller

- EZ-PD™ CCG3: Industry's Most Integrated Type-C Port Controller

- EZ-PD™ CCG4: Industry's First Dual-Port Type-C Port Controller

- EZ-PD™ CCG5: Cypress's second generation Dual-Port Type-C Port Controller

- EZ-PD™ CCG5C: Cypress's second generation Single-Port Type-C Port Controller

- EZ-PD™ CCG3PA: Cypress's USB Type-C Power Adapter / Power Bank Port Controller

- EZ-PD™ CCG6: Single port Type-C Port Controller with integrated Load Switch Controller

- EZ-PD™ CCG6F: Single port Type-C Port Controller with integrated Load Switch

- EZ-PD™ CCG6DF: Dual- Port Type-C Port Controller with integrated Load Switch

- EZ-PD™ CCG6SF: Single-Port Type-C Port Controller with integrated Load Switch

Visit the Cypress Type-C Controller web page for more details on these product families and a feature comparison.

#### 1.3 CCGx Host SDK

The CCGx Host Software Development Kit (SDK) is a software solution that allows users to harness the capabilities of the Type-C controllers from Cypress to create PD Port Controller applications for notebook computers, desktops etc.

The following applications are supported by the SDK:

- CCG5 based single port notebook PD controller solution.

- CCG5 based single port Thunderbolt/USB4 PD port controller solution.

- CCG5 based dual port notebook PD controller solution.

- CCG5 based dual port Thunderbolt/USB4 PD port controller solution.

- CCG5C based single port notebook PD controller solution.

- CCG5C based single port Thunderbolt/USB4 PD port controller solution.

- CCG6 based single port notebook PD controller solution.

- CCG6 based single port Thunderbolt/USB4 PD port controller solution.

- CCG6SF based single port notebook PD controller solution.

- CCG6SF based single port Thunderbolt/USB4 PD port controller solution.

- CCG6DF based dual port notebook PD controller solution.

- CCG6DF based dual port Thunderbolt/USB4 PD port controller solution.

In addition to the above projects, the Host SDK also provides the following solutions for compatibility with older SDK versions. These solutions are unchanged from the previously released SDK 3.3.1 version.

- CCG3 based single port notebook PD controller solution.

- CCG4 based single port notebook PD controller solution using 24-QFN part.

- CCG4 based single port notebook PD controller solution using 40-QFN part.

- CCG4 based dual port notebook PD controller solution.

The SDK provides a firmware stack compatible with Type-C and USB-PD specifications, along with the necessary drivers and software interfaces required to implement Notebook/Host applications using the CCG5, CCG5C, CCG6, CCG6DF, CCG3 and CCG4 PD controllers.

The key features of CCGx notebook port controller solutions are:

- Compliant to USB-PD specification Revision 3.0, Version 2.0

- Compliant to USB Type-C Specification Revision 2.0

- Supports Type-C VBUS Over-Voltage Protection (OVP) and Over-Current Protection (OCP).

- Supports OCP on VConn supply (CCG5, CCG5C, CCG6, CCG6SF and CCG6DF only).

- Supports VBUS Short-Circuit Protection (SCP) and Reverse-Voltage Protection (RCP) on CCG6, CCG6SF and CCG6DF devices.

- Support Over-Temperature Protection (OTP) on CCG6SF and CCG6DF devices.

- Support DisplayPort alternate mode as a DFP\_U/DFP\_D.

- Support Thunderbolt3 alternate mode in DFP and UFP roles.

- Support USB4 operation in DFP and UFP roles.

- Support Host Processor Interface (HPI) for runtime control of power profiles, modes etc.

- Support field firmware upgrades over I2C Interface.

- Support BC 1.2 power source (DCP/CDP) operation for charging devices through Type-C to Type-A cable adapters (CCG5, CCG5C and CCG6 only).

- Support USB Type-C Connector System Software Interface (UCSI v1.1) protocol.

- Support I2C slave interface and interrupt to notify Platform Controller (SoC) based on PD state changes.

- Support I2C master interface to configure Intel Retimers as required based on PD state changes.

PD stack, HPI and Intel Platform support in library form

Firmware sources for other blocks

Full-featured Notebook/Host Application

Release Notes

SDK User Guide

API Reference Guide (CHM and PDF)

PERMANE Binaries

HEX and CYACD files corresponding to all Reference Projects

Figure 1: CCGx Host SDK Components

The CCGx Host SDK consists of several basic components as shown in Figure 1.

The SDK also includes reference projects implementing standard Type-C applications and documentation that guides the user in customizing existing applications or creating new applications.

### 1.3.1 SDK Directory Structure

At the top level, the following folders are present:

- **Documentation**: The docs folder contains the EZ-PD™ CCGx Host SDK documentation, which includes release notes, user guide, and API reference guide.

- CapsuleDriver: The capsule driver folder contains the capsule reference driver source code and the user guide.

- **Firmware**: The Firmware folder contains the firmware stack sources, reference projects, and pre-built firmware binaries targeted for the Kits and reference designs from Cypress.

- o **binaries**: The binaries folder contains the pre-built firmware binaries

- projects: The projects folder contains the sources and PSoC Creator workspaces for the port controller designs.

- CYPD5125-40LQXI\_notebook: Single port Notebook PD port controller application using CCG5.

- CYPD5125-40LQXI\_notebook.cywrk: PSoC Creator workspace settings for the application.

- CYPD5125-40LQXI\_notebook.cydsn: PSoC Creator projects container directory.

- Bootloader: Bootloader binaries used in the application.

- common: Application specific source files.

- o **src**: General CCGx firmware sources and headers.

- lib: USB-PD stack, HPI and Intel platform support libraries.

- CYPD5125-40LQXI\_notebook.cyprj: PSoC Creator build settings for the application.

- backup\_fw.cydsn: Container for the reduced feature secondary (back-up) application which is combined with the main application.

- CYPD5126-40LQXI\_notebook: Single port Notebook PD port controller application using CCG5C.

- CYPD6125-40LQXI notebook: Single port Notebook PD port controller application using CCG6.

- CYPD5225-96BZXI\_notebook: Dual port Notebook PD port controller application using CCG5.

- CYPD5125-40LQXI\_notebook\_tbt: Single port USB4 DRD port controller application using CCG5.

- CYPD5126-40LQXI\_notebook\_tbt: Single port USB4 DRD port controller application using CCG5C.

- CYPD6125-40LQXI\_notebook\_tbt: Single port USB4 DRD port controller application using CCG6.

- CYPD5225-96BZXI\_notebook\_tbt: Dual port USB4 DRD port controller application using CCG5.

- CYPD6227-96BZXI\_notebook\_dualapp: Notebook PD port controller application using CCG6SF (single port) or CCG6DF (dual port).

- CYPD6227-96BZXI\_notebook\_dualapp\_tbt: USB4 DRD port controller application using CCG6SF (single port) or CCG6DF (dual port).

- CYPD6227-96BZXI\_notebook\_tbt: USB4 DRD port controller application using CCG6SF (single port) or CCG6DF (dual port).

- CYPD3125-40LQXI\_notebook: Single port Notebook PD port controller using CCG3

- CYPD3126-42FNXI\_notebook: Single port Notebook PD port controller using CCG3

- CYPD4126-24LQXI\_notebook: Single port Notebook PD port controller using CCG4

- CYPD4126-40LQXI\_notebook: Single port Notebook PD port controller using CCG4

- CYPD4226-40LQXI\_notebook: Dual port Notebook PD port controller using CCG4

The src folder inside each reference application has the following sub-folders:

- app: The app folder contains the top-level application layer functionality that implements the required USB-PD controller functions. This includes functionality such as PDO evaluation and contract negotiation, fault detection and handling, BC 1.2 charging support etc.

- o app/alt\_mode: The alternate mode specific implementation can be found in this directory.

- app/intel\_tbt: This folder contains the headers for the Intel Platform support including I2C slave interface to the Platform SoC and I2C master interface to control retimers.

- hpiss: The hpiss folder contains the API interface definition for the Host Processor Interface implemented by the CCGx firmware.

- pd\_common: The pd\_common folder contains the headers for the core Type-C and USB-PD stack for the CCGx device. This includes the HAL, the Type-C port manager, the USB-PD protocol layer, the USB-PD policy engine, and the Device Policy Manager.

- pd\_hal: The pd\_hal folder contains the low-level driver header and source files for USB-PD hardware block.

- scb: The scb folder contains the API interface definition for the dedicated I2C slave driver using the Serial Controller Blocks (SCB) on the CCGx device. Since I2C slave mode is the most commonly-used interface for CCGx, a specially optimized driver is provided for the same.

- system: The system folder contains header and source files relating to the CCGx device hardware and registers, bootloader and flash access functions, low-level drivers for the GPIO blocks on the CCGx device, and a soft timer implementation that is used by the firmware stack.

- ucsi: The ucsi folder contains implementation of the USB Type-C Connector System Software Interface (UCSI v1.1). The UCSI protocol is implemented on top of the HPI I2C slave interface using separate registers and commands.

Figure 2 shows the installed directory structure of the CCGx Host SDK, along with descriptions for all of the important folders.

Figure 2: CCGx Host SDK Directory Structure

```

EZ-PD CCGx Host SDK

CCGx Host SDK Directory

L_CCG<sub>X</sub>

CCGx Host Directory

-Documentation

Documentation: User guide, API guide etc.

-CapsuleDriver

CapsuleDriver: Reference driver source code and User

auide.

L-Firmware

-binaries

Pre-built firmware binaries

└projects

Reference Projects

CYPD3125-40LQXI notebook

CCG3 based Notebook PD controller project

CCG3 based Notebook PD controller project

---CYPD4126-24LQXI notebook

CCG4 (24-QFN) based Notebook PD controller project

----CYPD4126-40LQXI notebook

CCG4 based single port Notebook PD controller project

----CYPD4226-40LQXI notebook

CCG4 based single port Notebook PD controller project

---CYPD5125-40LQXI notebook

CCG5 based single port Notebook PD controller project

CCG5 based single port USB4 DRD controller project

---CYPD5225-96BZXI notebook

CCG5 based dual port Notebook PD controller project

-CYPD5225-96BZXI_notebook_tbt

CCG5 based dual port USB4 DRD controller project

-CYPD5126-40LQXI notebook

CCG5C based Notebook PD controller project

CCG5C based USB4 DRD controller project

---CYPD6125-40LQXI notebook

CCG6 based Notebook PD controller project

—CYPD6125-40LQXI_notebook_tbt CCG6 based USB4 DRD controller project

—CYPD6227-96BZXI_notebook_dualapp CCG6DF based Notebook PD controller project

CCG6DF based USB4 DRD controller project

---CYPD6227-96LZXI notebook tbt

```

## 2. SDK Installation

### 2.1 SDK Installation

Once installed, the directory structure will be as shown in Figure 2.

### 2.2 Tool Dependencies

#### 2.2.1 PSoC Creator

Cypress's Type-C controllers are based on Cypress's PSoC® 4 programmable system-on-chip architecture, which includes programmable analog and digital blocks, an ARM® Cortex®-M0 core, and internal flash memory.

The PSoC Creator IDE is used for configuring the CCGx devices, to develop and compile the firmware applications and optionally to program the devices using SWD. This version of the SDK requires PSoC Creator 4.3 (4.3 Build 34) or higher.

This version of PSoC Creator can be installed and used on a computer along with previous versions of PSoC Creator.

The PSoC Creator release includes the GNU ARM compiler tools.

### 2.2.2 ARM MDK Compiler and Tools

All reference projects in the Host SDK require the ARM MDK tools (<a href="http://www2.keil.com/mdk5/">http://www2.keil.com/mdk5/</a>) for compilation. Please obtain a license for the MDK toolchain from ARM to work with these projects.

Trying to compile the projects using the GNU ARM tools provided with PSoC Creator will results in build errors due to firmware binary size that exceeds the device flash memory constraints.

### 2.2.3 Python

The USB4/Thunderbolt host reference projects make use of a set of Python scripts to customize the binaries at the end of build process. These Python scripts are invoked as part of the build process itself and will result in build failure is Python is not installed on the computer.

Please install Python 3.7 or later from <a href="https://www.python.org/downloads/">https://www.python.org/downloads/</a> to ensure that these post-build steps can work properly.

### 2.2.4 EZ-PD Configuration Utility

The CCGx devices are shipped with a pre-programmed bootloader that allows the firmware on the device to be updated through an I<sup>2</sup>C interface, the CC channel or the USB interface, which is part of the Type-C interface. All of the parts supported by the Host SDK make use of an I<sup>2</sup>C bootloader, which means that firmware updates are done through the I<sup>2</sup>c interface.

The EZ-PD Configuration Utility is a Windows-based application, which can be used to program the CCGx devices on Cypress-provided kits (DVKs and EVKs) through the bootloader interface.

The EZ-PD Configuration Utility relies on a Cypress USB controller, which can connect to the CCGx device through I<sup>2</sup>C for programming. Therefore, it will only work with the Cypress-provided kits or other hardware, which includes the Cypress USB – I<sup>2</sup>C bridge devices.

The EZ-PD Configuration Utility is also used for creating custom configurations for the CCGx firmware application, which includes aspects such as the supported power profiles, protection schemes, and so on.

This version of the SDK requires the latest EZ-PD Configuration Utility version 1.3.1, which includes support for programming and configuring CCG2, CCG3, CCG4, CCG5, CCG5C, CCG6, CCG6DF and CCG6xF devices.

### 2.3 Hardware Dependencies

The CY4531 kit (http://www.cypress.com/documentation/development-kitsboards/cy4531-ez-pd-ccg3-evaluation-kit) can be used to evaluate the CCG3 firmware solution.

The CY4541 kit (<a href="http://www.cypress.com/documentation/development-kitsboards/cy4541-ez-pdtm-ccg4-evaluation-kit-guide">http://www.cypress.com/documentation/development-kitsboards/cy4541-ez-pdtm-ccg4-evaluation-kit-guide</a>) can be used to evaluate the CCG4 firmware solutions. The kit ships with the CYPD4225-40LQXI controller which supports only USB-PD 2.0 by default. The CCG4 device on the board can be swapped with CYPD4126-40LQXI or CYPD4226-40LQXI devices to work with the projects in the SDK.

Cypress does not provide Evaluation Kits for CCG5, CCG5C, CCG6, CCG6SF or CCG6DF devices at present. CCG5, CCG5C, CCG6, CCG6SF and CCG6DF solutions should use the reference schematics available in the respective datasheets.

## 3. Getting Started with CCGx Host SDK

### 3.1 Preparing to use PSoC Creator

### 3.1.1 Environment Updates

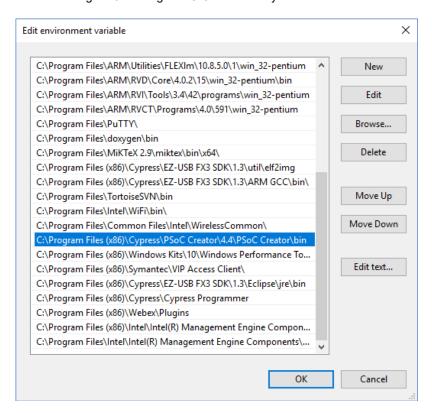

Many of the reference projects in the CCGx Host SDK make use of a post-build script which combines code from multiple projects into a single binary. These scripts make use of the CyElfTool.exe application which is part of the PSoC Creator installation. To enable the projects to locate the executable and run successfully, the path where PSoC Creator has been installed needs to be added to the PATH environment variable in the system.

Figure 3 shows the PATH variable updated to add the standard install path for PSoC Creator 4.4. If you have installed PSoC Creator at a different location, please use the appropriate path.

Figure 3: Adding PSoC Creator binary folder to PATH

### 3.2 Using the Reference Projects

As Figure 2 shows, the SDK includes reference projects for the target applications that can be used to obtain a jump-start in the process of developing a CCGx based notebook port controllers (notebook, for short) applications.

This version of SDK provides the following reference projects for the following applications:

- CYPD5125-40LQXI\_notebook: This project implements a single Type-C port controller for notebook platforms using the CYPD5125-40LQXI (CCG5) device.

- CYPD5125-40LQXI\_notebook\_tbt: This project implements a single Type-C port controller for USB4 Dual-Role Device (DRD) platforms using the CYPD5125-40LQXI (CCG5) device.

- CYPD5126-40LQXI\_notebook: This project implements a single Type-C port controller for notebook platforms using the CYPD5126-40LQXI (CCG5C) device.

- 4. **CYPD5126-40LQXI\_notebook\_tbt:** This project implements a single Type-C port controller for USB4 DRD platforms using the CYPD5126-40LQXI (CCG5C) device.

- CYPD5225-96BZXI\_notebook: This project implements a dual Type-C port controller for notebook platforms using the CYPD5225-96BZXI (CCG5) device.

- CYPD5225-96BZXI\_notebook\_tbt: This project implements a dual Type-C port controller for USB4 DRD platforms using the CYPD5225-96BZXI (CCG5) device.

- CYPD6125-40LQXI\_notebook: This project implements a single Type-C port controller for notebook platforms using the CYPD6125-40LQXI (CCG6) device.

- 8. **CYPD6125-40LQXI\_notebook\_tbt:** This project implements a single Type-C port controller for USB4 DRD platforms using the CYPD6125-40LQXI (CCG6) device.

- CYPD6227-96BZXI\_notebook\_dualapp: This project implements a dual Type-C port controller for notebook platforms using the CYPD6227-96BZXI (CCG6DF) device. This project also generates a binary that implements a single Type-C port controller for notebook platforms using the CYPD6127-48LQXI (CCG6SF) device.

- CYPD6227-96BZXI\_notebook\_dualapp\_tbt: This project implements a dual Type-C port controller for USB4 DRD platforms using the CYPD6227-96BZXI (CCG6DF) device. This project also generates a binary that implements a single Type-C port controller for USB4 DRD platforms using the CYPD6127-48LQXI (CCG6SF) device.

- 11. CYPD6227-96BZXI\_notebook\_tbt: This project implements a dual Type-C port controller for USB4 DRD platforms using the CYPD6227-96BZXI (CCG6DF) device. This project also generates a binary that implements a single Type-C port controller for USB4 DRD platforms using the CYPD6127-48LQXI (CCG6SF) device. This version of the USB4 DRD implementation uses a different boot architecture as compared to the CYPD6227-96BZXI notebook dualapp tbt project.

- 12. **CYPD3125-40LQXI\_notebook**: This project implements a single Type-C port controller for notebook platforms using the CYPD3125-40LQXI (CCG3) device. Please note that the CCG3 Notebook DRP firmware is in maintenance mode and has not been updated since the Host SDK 3.3.1 release.

- 13. **CYPD3126-42FNXI\_notebook**: This project implements a single Type-C port controller for notebook platforms using the CYPD3126-42FNXI (CCG3) device. Please note that the CCG3 Notebook DRP firmware is in maintenance mode and has not been updated since the Host SDK 3.3.1 release.

- 14. **CYPD4126-24LQXI\_notebook**: This project implements a single Type-C port controller for notebook platforms using the CYPD4126-24LQXI (CCG4) device. Please note that the CCG4 Notebook DRP firmware is in maintenance mode and has not been updated since the Host SDK 3.3.1 release.

- 15. **CYPD4126-40LQXI\_notebook**: This project implements a single Type-C port controller for notebook platforms using the CYPD4126-40LQXI (CCG4) device. Please note that the CCG4 Notebook DRP firmware is in maintenance mode and has not been updated since the Host SDK 3.3.1 release.

- 16. CYPD4226-40LQXI\_notebook: This project implements a dual Type-C port controller for notebook platforms using the CYPD4226-40LQXI (CCG4) device. Please note that the CCG4 Notebook DRP firmware is in maintenance mode and has not been updated since the Host SDK 3.3.1 release.

Each reference project is provided in the form of a PSoC Creator workspace. The workspace can be opened using the PSoC Creator and the projects can be customized and compiled.

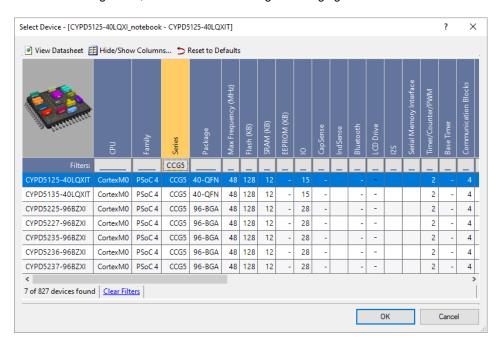

**Note:** These projects are designed to work with specific devices mentioned above. Changing the target part number using Device Selector will cause the firmware build to fail.

### 3.2.1 Copying the Project with PSoC Creator

PSoC Creator allows SDK example projects to be copied to a different location without affecting the original installed files. There are mainly two ways of doing this: using the Start Page to copy the workspaces and using the Code Examples.

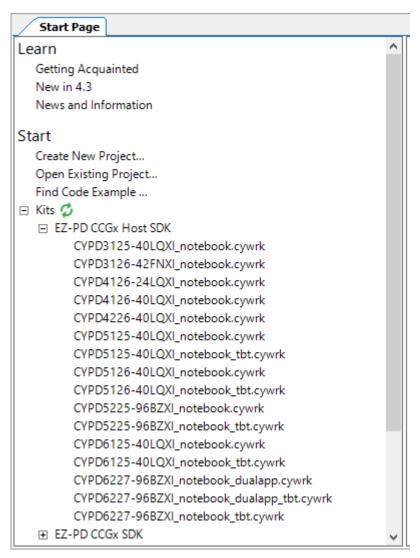

#### 3.2.1.1 From Start Page

The SDK example projects are listed under *Kits* → *EZ-PD CCGx Host SDK* on the Start Page. Click on the workspace name to copy it. When copying the workspace, the complete workspace directory along with all the projects associated with the workspace are copied to the selected destination location. PSoC Creator automatically opens the copied workspace after completing the copy. Figure 4 shows the startup page for PSoC Creator, expanded to show the reference firmware projects provided with EZ-PD CCGx Host SDK.

Figure 4: PSoC Creator Startup Page

Note: If Start Page is not open, it can be accessed via View->Other Windows->Start Page.

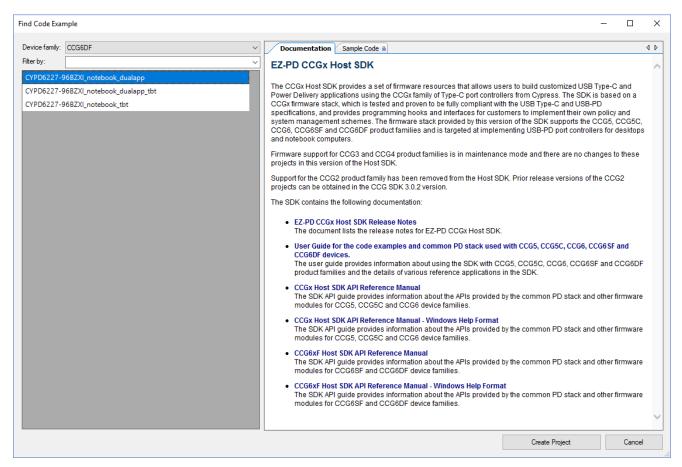

#### 3.2.1.2 From Code Examples

PSoC Creator lists the SDK examples under the Code Examples Dialog. This dialog can be accessed via *File->Code Example ...* or during new project creation.

Figure 5: PSoC Creator Code Examples Dialog

Figure 5 shows the example projects from Code Examples Dialog. The required Device Family can be selected to narrow down the list of examples and the required project can be copied by clicking the *Create Project* button. When using Code Examples Dialog to copy the project, the complete project directory and the selected project shall be copied. It should be noted that the workspace and the files outside the project directory are not copied. All files required for the SDK examples projects are under the project directory and so this behavior shall not have any impact.

**Note:** Since a common code example is used to generate binaries for CCG6DF and CCG6SF devices, use the CCG6DF device family to locate and select the reference project for CCG6SF devices as well.

**Note:** The bootloader project shall not be present in the workspace created through the code example dialog, and shall require to be explicitly added to the workspace. These projects will still be available under the project root folder and you can use the **File**  $\rightarrow$  **Add**  $\rightarrow$  **Existing project** option to add them to the workspace.

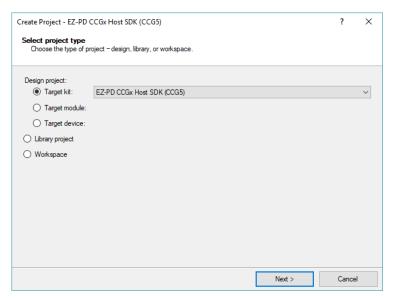

The File → New → Project menu option also allows you to create a new project based on existing example projects. Choose the desired device from the list of EZ-PD CCGx Host SDK items as the Target Kit in the Create Project dialog as shown in Figure 6.

Figure 6: Selection of Target Kit for creation on new project

Then choose Code Example and select the desired code example as shown in Figure 5.

**Note:** When copying via Create Project option, a wrong device part number may get selected. In this case, the user is expected to change the part number to correct one using **Device Selector Dialog**.

### 3.2.2 Compiling the Project with PSoC Creator

This section walks you through the procedure to open the reference projects and build them using PSoC Creator. The CYPD5125-40LQXI\_notebook project is used as an illustration in the following descriptions.

### 3.2.2.1 Selecting the Compiler Toolchain

The code examples provided in the Host SDK can only be compiled using ARM MDK toolchain (µVision V5.25 or later). Since the CCGx parts supported by the SDK have up to 128 KB of flash, a full version of the MDK tools is required to make use of this option.

The following steps should be followed to build the code examples using the MDK toolchain.

- 1. Download and install MDK from <a href="http://www2.keil.com/mdk5">http://www2.keil.com/mdk5</a>. A limited period evaluation license can be used or a full license can be purchased from ARM.

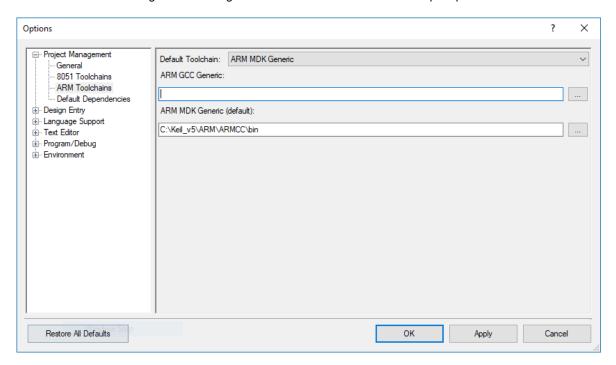

- 2. Provide the path to the ARM compiler toolchain in the PSoC Creator settings, by using the Project Management → ARM Toolchains option under the Tools → Options menu, as shown in Figure 7.

Figure 7: Pointing PSoC Creator to the ARM MDK compiler path

### 3.2.2.2 Compiling the Reference Project

The following steps describe the process to compile the reference project and generate the binaries using the PSoC Creator IDE and the ARM MDK tool-chain.

- 1. Navigate to the project folder using Windows Explorer. The project folder contents will look as shown in Figure 8.

- The CYPD5125-40LQXI\_notebook.cywrk file is the PSoC Creator workspace file that can be opened using the PSoC Creator IDE. If you have installed multiple Creator versions, ensure that the appropriate PSoC Creator version (Creator 4.3 or later) is used to open the workspace.

Name Date modified Size Type 7/8/2020 1:22 PM File folder backup\_fw.cydsn Bootloader 7/8/2020 1:22 PM File folder 7/8/2020 1:22 PM File folder 7/8/2020 1:22 PM dummy\_boot.cydsn File folder i2c\_boot.cydsn 7/8/2020 1:22 PM File folder lib 7/8/2020 1:22 PM File folder 7/8/2020 1:22 PM noboot.cydsn File folder 7/8/2020 1:22 PM File folder TopDesign 7/8/2020 1:22 PM File folder 17 KB cm0gcc.ld 7/6/2020 10:30 AM LD File cm0mdk.scat 7/6/2020 10:30 AM SCAT File 8 KB config.h 7/6/2020 10:30 AM H File 14 KB cyapicallbacks.h 7/6/2020 10:30 AM H File 3 KB CYPD5125-40LQXI\_notebook.cydwr 7/6/2020 10:30 AM CYDWR File 25 KB CYPD5125-40LQXI\_notebook.cyprj 7/6/2020 10:34 AM PSoC Creator Proj... 200 KB post\_build.bat 7/6/2020 10:34 AM Windows Batch File 2 KB

Figure 8: Contents of the Reference Project Folder

3. Once you open the workspace, note that there are three projects:

- a. CYPD5125-40LQXI\_notebook.cydsn: This is the main firmware project for the application. This application is designed to work on top of the bootloader pre-programmed on the CCG5 device. More details on this project are provided in later sections.

- b. backup\_fw.cydsn: This is a limited feature version of the notebook PD port controller application using the CCG5 device. This is used as a secondary firmware binary which allows recovery in case the device firmware gets corrupted during an upgrade process.

- c. noboot.cydsn: The main firmware project in CYPD5125-40LQXI\_notebook.cydsn does not support runtime debugging through the SWD interface. The noboot.cydsn is a version of the same firmware application, which does not depend on the bootloader. This firmware overwrites the complete device flash and expects that the device will be programmed through SWD.

**NOTE:** If the project was copied using Code Examples, then only the main project shall be seen on the workspace. The other two projects can be added to the workspace using **Add Existing Project** option.

There is a fourth project available (*i2c\_boot.cydsn*) in the project workspace directory. This is the bootloader project available for reference. The pre-built bootloader binary from the Bootloader directory should be used unless boot flow modifications are required. This project is not added to the workspace and can be added using *Add Existing Project* option.

- 4. The CYPD5125-40LQXI\_notebook.cydsn project is set as the default project for the workspace. Choose the Build CYPD5125-40LQXI\_notebook menu option from the Build menu or the pop-up menu obtained by right-clicking on the project name.

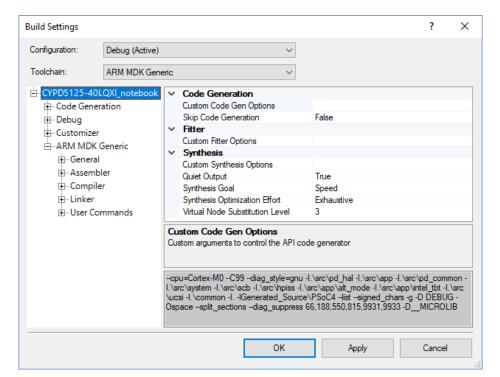

- Ensure that the compiler Toolchain is set to ARM MDK Generic. This can be verified / modified in the Build settings for the project. The Build Settings Dialog can be opened by right clicking the corresponding project. Figure 9 shows the Build Settings Dialog.

Figure 9: Project Build Settings Dialog

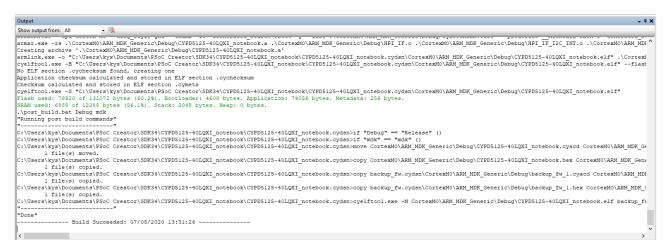

6. You may receive a pop-up window asking for permission to make the project file writeable. Select **Yes** to allow the project build to go through. The complete build process may take about two to three minutes. The output window at the bottom of the IDE will look as shown in Figure 10 at the end of the build process.

Figure 10: Output Window after the Build is Complete

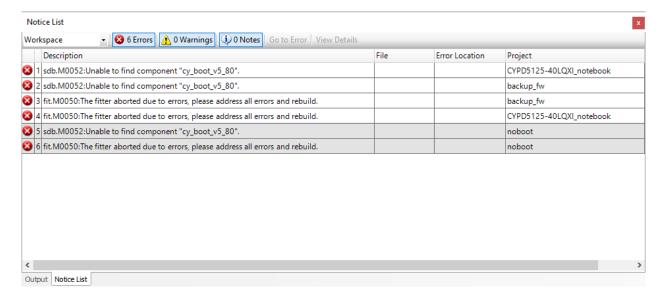

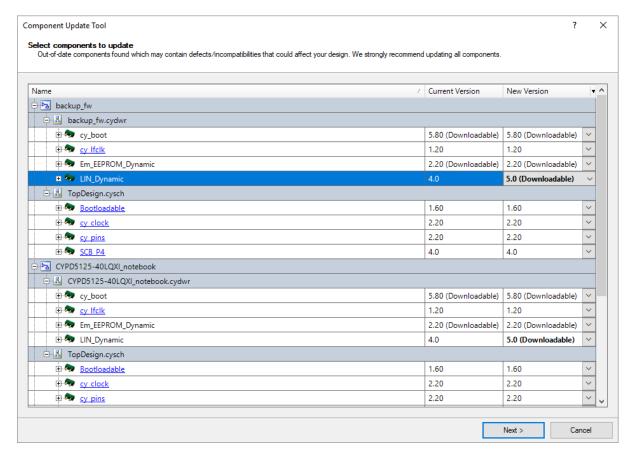

7. The build process may throw errors due to missing Creator components as shown in Figure 11. This error can be resolved by right-clicking on the Workspace name and selecting Update Components. A Component Update Tool dialog as shown in Figure 12 will pop up. Select Next and then Finish to allow PSoC Creator to download the latest component versions. This update sequence will only need to be completed on the first Host SDK project that you compile.

Figure 11: Build error due to missing Creator Components

Figure 12: Component update tool dialog showing available updates

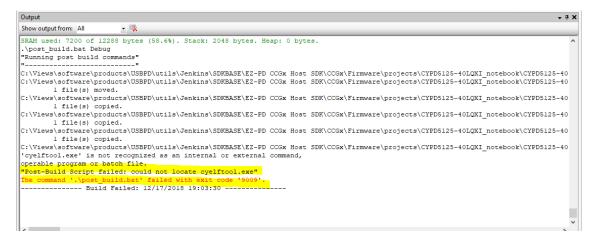

8. If the post build script which combines the backup and primary firmware images throws an error as shown in Figure 13, please add the PSoC Creator binary folder to the PATH variable in the system environment and then restart PSoC Creator. Please refer to Section 3.1.1 for more details.

Figure 13: Post-build script error in reference projects

- 9. Now, navigate to the project folder using Windows Explorer to locate the compiled firmware binaries. Navigate to the CYPD5125-40LQXI\_notebook.cydsn\CortexM0\ARM\_MDK\_Generic\Debug folder for the output files. The following three files are the most important output files generated by the build process:

- a. **CYPD5125-40LQXI\_notebook.hex**: This is an SWD programmable binary file in the Intel Hex format that combines the bootloader as well as the notebook port controller firmware application.

- b. **CYPD5125-40LQXI\_notebook\_2.cyacd**: This binary file contains the full-featured firmware application that can be loaded to the CCG5 device flash through the I2C interface. The format of the file is documented here. The EZ-PD Configuration Utility accepts firmware binaries in the cyacd format and programs them to the CCG5 device.

- c. CYPD5125-40LQXI\_notebook\_1.cyacd: This binary file contains the limited feature backup firmware application that can be loaded to the CCG5 device flash through the I2C interface. The format of the file is documented here. The EZ-PD Configuration Utility accepts firmware binaries in the cyacd format and programs them to the CCG5 device.

### 3.2.3 Programming CCGx using the EZ-PD Configuration Utility

If the CCG5 evaluation board is being used, the firmware binaries built using the above procedure can be loaded on to the CCG5 device using the EZ-PD Configuration Utility. This section provides step-by-step instructions for updating the firmware with the EZ-PD Configuration Utility. Refer to the EZ-PD Configuration Utility User Manual for more details.

- 1. Power up the CCG5 evaluation board using the 20V power adapter and connect a USB cable from the Mini-B connector to the host PC.

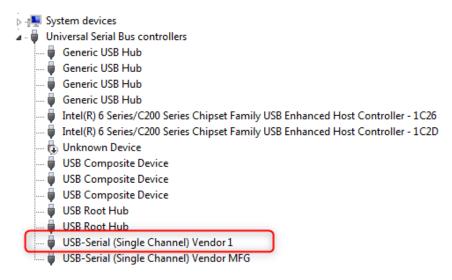

- Wait for driver detection and binding for the USB-Serial controller on the board. The driver for this controller can be obtained by searching on Windows Update. Once the driver binding is successful, a "USB-Serial (Single Channel) Vendor 1" device will be listed under 'Universal Serial Bus Controllers' in the **Device Manager** window. See Figure 14 for the expected device listing.

Figure 14: Device Manager View Showing USB-Serial Bridge Device

- If the automatic driver installation does not succeed, you can download and use the Cypress USB Serial Windows Driver Installer. Refer to the USB-Serial Windows Driver Installation Guide document as well.

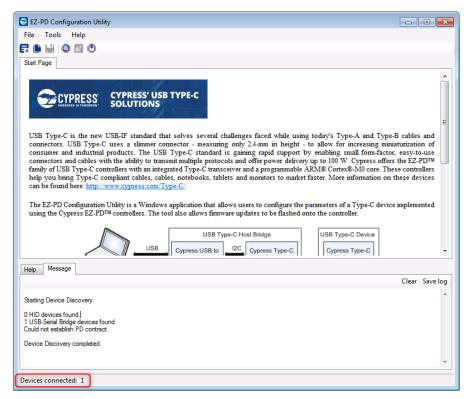

- 4. Open the EZ-PD Configuration Utility GUI. If the device driver binding is successful, the GUI should report a device connected on the lower border of the UI as shown in Figure 15.

Figure 15: Configuration Utility Detecting the Connected CCG5 evaluation board

- Go to Tools → Firmware Update. The utility detects and identifies the device at this stage. A firmware update dialog

appears at the end of this process (see Figure 16).

- 6. When you click on the required node (**Notebook**) in the device tree, the UI displays information about the CCGx device and the current firmware running on it.

Read From Device ? X Refresh Select Target Devices Part number: CYPD5126-40LQXI ■ USB-Serial [Single Channel] (0) Device family: CCG5C ■ NOTEBOOK Application type: NOTEBOOK Running mode: Bootloader Base version: 3.2.1.56 App version: 0.1 Firmware-1 Base version: 3.4.0.2473 App version: Base version: 3.4.0.2473 App version: 0.0 Programmable: Configuration from FW:1 will be read Use bootloader to read

Figure 16: Firmware Update Dialog

- Navigate to the folder containing the firmware binaries generated during the firmware build, and select the CYPD5125-40LQXI\_notebook\_1.cyacd and CYPD5125-40LQXI\_notebook\_2.cyacd files in the two firmware path options in the dialog.

- 8. Check the "Use bootloader to flash" option so that both banks of firmware can be updated in one step; and click on the **Program** button to start the firmware update. The full update will take about 30 seconds.

- Once the update process is complete, use the Tools > Read from Device option to bring up a dialog that can show

the current firmware version. If the firmware project from the SDK is used without any changes, the new running

firmware version should match the version of firmware downloaded.

- 10. Since the Firmware-2 binary is the full-featured application, the CCG5 bootloader is designed such that it loads the Firmware-2 whenever it is present (independent of the firmware version).

### 3.3 Updating CCGx Configuration

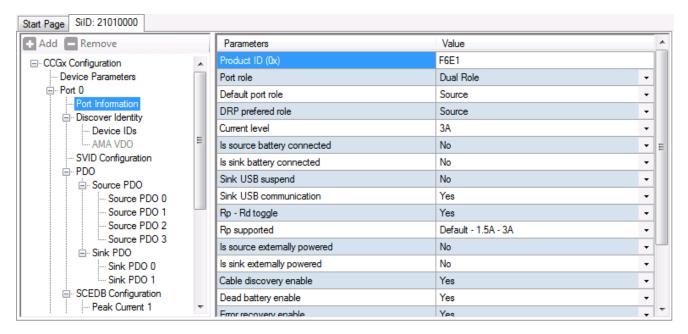

### 3.3.1 Configuration Parameters

The CCGx firmware design uses a configuration table, which specifies several parameters that control device functionality. These parameters include:

- The VDM responses sent by the device for various PD messages.

- The power profiles supported by the device as a provider and as a consumer.

- The port roles supported by the device (Source/Sink/Dual Role).

- Enable/disable flags and parameters that control the various firmware features.

These parameters are stored in a configuration table so that they can be updated/customized without updating the firmware. The utility provides an interactive GUI through which all of the contents of the configuration table can be updated.

Table 1 shows the list of configuration parameters which are relevant to the various Notebook/Host PD port controller solutions. Refer to the EZ-PD Configuration Utility User Manual for a description of the various UI screens presented by the utility to configure these parameters. Each UI screen also provides tool-tips that guide you through the process of defining the firmware configuration.

Please note that changing the Source PDO configuration is not recommended while using the EVKs because the default settings in the solution correspond to the actual kit hardware design.

Table 1: List of Configuration parameters for Host Applications

| Configuration Parameter    | Description                                                                                                                                                  | Default Value                  | Change Allowed                                                                    |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------|

| Device Parameters          |                                                                                                                                                              |                                |                                                                                   |

| Part Number                | CCG MPN used in the project.                                                                                                                                 | <as per<br="">Project&gt;</as> | Select the part number matching the application.                                  |

| Manufacturer Info          | String used in the PD 3.0 Manufacturer Info message.                                                                                                         | "Cypress"                      | Can be changed.                                                                   |

| Vendor ID                  | Vendor ID value used in the ID Header VDO, Manufacturer Info and Source Capabilities Extended messages.                                                      | 0x04B4                         | Can be changed.                                                                   |

| Config table major version | Config table format revision. Used by firmware to ensure compatibility.                                                                                      | 2                              | The version of the configuration table format. Leave this with the default value. |

| PD revision                | USB-PD spec revision supported by the firmware.  Note: This parameter only affects the UI behavior and does not change firmware functionality. The parameter | 3.0                            | Set based on firmware features.                                                   |

|                              | value should be based on the actual feature selection in the firmware binary.                                                                                                                     |                                |                                              |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------|

| Cable discovery count        | Number of cable discovery attempts to be made                                                                                                                                                     | 0x14                           | Can be changed in the range of 1 to 20.      |

| Dead battery event mask (0x) | Default value of HPI event mask that will be applied to all PD ports on the device.                                                                                                               | 0x0000                         | Can be changed.                              |

| Port Information             |                                                                                                                                                                                                   |                                |                                              |

| Product ID                   | Product ID used in Product VDO,<br>Source Capabilities Extended and<br>Manufacturer Info messages.                                                                                                | <as per<br="">Project&gt;</as> | The USB Product ID assigned for the product. |

| Port role                    | Power role configuration for the port:<br>Sink, Source or Dual Role                                                                                                                               | Dual role                      | Change not recommended for a host platform.  |

| Default port role            | Determines the start-up state used by the Type-C state machine when the port role is DRP.  Note: Changing this parameter does not guarantee the port role used when there is a Type-C connection. | Source                         | Change not recommended for a host platform.  |

| DRP preferred role           | Enable Source or Sink preference on a DRP port.                                                                                                                                                   | Source                         | Change not recommended for a host platform.  |

| Current level                | Choose the Rp current source used as a Type-C source.                                                                                                                                             | ЗА                             | Can be changed.                              |

| Is source battery connected  | Legacy parameter: Don't care in current stack.                                                                                                                                                    | No                             | Don't care                                   |

| Is sink battery connected    | Legacy parameter: Don't care in current stack.                                                                                                                                                    | No                             | Don't care                                   |

| Sink USB suspend             | Determines the No USB Suspend bit in the request message sent by the CCGx device.                                                                                                                 | No                             | Can be changed.                              |

| Sink USB communication       | Determines the USB Communications capable bit in PD messages.                                                                                                                                     | Yes                            | Change not recommended.                      |

| Rp-Rd Toggle                 | Whether DRP port should use automatic Rp-Rd toggle sequence.                                                                                                                                      | Yes                            | Should be YES for DRP ports.                 |

| Rp supported                 | Bit-map representing supported Rp current source values. The actual Rp value can be chosen from this list at run-time through the HPI interface.                                                  | Default, 1.5A<br>and 3.0A      | Can be changed                               |

| Is source externally powered | Whether the power source is externally powered.                                                                                                                                                   | No                             | Can be changed based on system design.       |

| Is sink externally powered   | Whether the power sink is externally powered.  Note: Should be set to the same value as Is source externally powered.                                                                             | No                             | Can be changed based on system design.       |

| Cable discovery enable       | Whether cable discovery is enabled. Power supply will be limited to 3A when cable discovery is not enabled.                                                                                       | Yes                            | Change not recommended                       |

| Dead battery enable          | Whether Type-C state machine should directly transition to Attached.SNK state if VBus is present on power-up.                                                                                     | Yes                            | Change not recommended                       |

| Error recovery enable     | Whether Type-C error recovery sequence is enabled.                                                                                                     | Yes                         | Change not recommended                                            |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------|

| DR_SWAP response          | Default response to be used for DR_SWAP requests.                                                                                                      | ACCEPT                      | Can be changed                                                    |

| PR_SWAP response          | Default response to be used for PR_SWAP requests.                                                                                                      | ACCEPT                      | Can be changed                                                    |

| VCONN_SWAP response       | Default response to be used for VCONN_SWAP requests to become VConn source.  Swap to allow the port partner to become VConn source is always accepted. | ACCEPT                      | Can be changed                                                    |

| FRS Enable                | Whether Fast Role Swap as source (sink → source) is enabled.                                                                                           | FRS Receive                 | Can be set to FRS receive or None. FRS transmit is not supported. |

| VConn retain              | Whether the port should continue to supply VConn even if the AMA or Cable reports that VConn supply is not required.                                   | No                          | Can be changed.                                                   |

| Device IDs                |                                                                                                                                                        |                             |                                                                   |

| USB host support          | Whether the port implements a USB host controller.                                                                                                     | Yes                         | Should be Yes for desktops and notebooks.                         |

| USB device support        | Whether the port implements a USB device.                                                                                                              | No                          | Should be No for desktops and notebooks.                          |

| Modal operation supported | Whether any Type-C alternate modes are supported as an UFP.                                                                                            | Yes                         | Set this to No if no UFP alternate modes are required.            |

| USB Vendor Id             | Vendor ID. Copied from the Device parameters screen.                                                                                                   | 0x04B4                      | This gets changed through Port Information node.                  |

| Product type (UFP)        | Product type to be reported as an UFP.                                                                                                                 | Peripheral                  | Can be changed                                                    |

| Product type (DFP)        | Product type as a DFP.                                                                                                                                 | Host                        | Change not recommended                                            |

| USB-ID compliance XID     | XID value to be used in the Cert Stat VDO.                                                                                                             | 0                           | Can be changed                                                    |

| USB Product ID            | Product ID. Copied from the Device parameters screen.                                                                                                  | <as per="" project=""></as> | This gets changed through Port Information node.                  |

| Bcd device                | BCD Device value to be reported in Product VDO.                                                                                                        | 0                           | Can be changed                                                    |

| UFP VDO 1                 |                                                                                                                                                        |                             |                                                                   |

| UFP VDO version           | Version Number of the VDO                                                                                                                              | 0                           | Should not be changed                                             |

| USB 2.0 device capability | Is device USB 2.0 capable                                                                                                                              | Capable                     | Can be changed                                                    |

| USB 3.2 device capability | Is device USB 3.2 capable                                                                                                                              | Capable                     | Can be changed                                                    |

| USB 4 device capability   | Is device USB 4 capable                                                                                                                                | Capable                     | Can be changed                                                    |

| TBT3 mode enable          | Support of TBT3 data mode                                                                                                                              | Yes                         | Can be changed                                                    |

| Other data mode enable    | Enable/disable Alternate Modes that reconfigure the signals on the USB Type-C connector (except for TBT3)                                              | No                          | Can be changed                                                    |

| Custom mode enable        | Enable/disable Alternate Modes that do not reconfigure the signals on the USB Type-C connector.                                                        | No                          | Can be changed                                                    |

| USB Highest Speed                     | The USB Highest Speed field shall indicate the port's highest signaling capability. | Gen3                 | Can be changed          |

|---------------------------------------|-------------------------------------------------------------------------------------|----------------------|-------------------------|

| UFP VDO 2                             | - Capability.                                                                       |                      |                         |

| USB4 Min Power (W)                    | Minimum power in watts required to function in USB4 operation                       | 15                   | Can be changed          |

| USB4 Max Power (W)                    | Maximum power in watts required to function in USB4 operation                       | 15                   | Can be changed          |

| USB3 Min Power (W)                    | Minimum power in watts required to function in USB3 operation                       | 15                   | Can be changed          |

| USB3 Max Power (W)                    | Maximum power in watts required to function in USB3 operation                       | 15                   | Can be changed          |

| DFP VDO                               |                                                                                     |                      |                         |

| DFP VDO version                       | Version Number of the VDO                                                           | 0                    | Should not be changed   |

| USB 2.0 host capability               | Is host USB 2.0 capable                                                             | Capable              | Can be changed          |

| USB 3.2 host capability               | Is host USB 3.2 capable                                                             | Capable              | Can be changed          |

| USB 4 host capability                 | Is host USB 4 capable                                                               | Capable              | Can be changed          |

| Port Number                           | Unique port number to identify a specific port on a multi-port device               | 0                    | Can be changed          |

| Source PDO 0                          |                                                                                     |                      |                         |

| Dual role power                       | Both power source and sink functions are supported.                                 | Yes                  | Can be changed          |

| USB suspend support                   | USB link suspend is supported                                                       | No                   | Can be changed          |

| USB communication capable             | USB host or device function is supported                                            | Yes                  | Can be changed          |

| Data role swap                        | Data role swap is supported                                                         | Yes                  | Can be changed          |

| Unchunked extended messages supported | Device support send and receive extended messages in a single unchunked message     | Yes                  | Should not be changed   |

| Peak current (0x)                     | Additional peak current source capability. See USB-PD Spec for encoding             | 0                    | Can be changed          |

| Voltage (mV)                          | Output voltage level in mV units                                                    | 5000                 | Can't be changed        |

| Maximum current (mA)                  | Maximum current that can be sourced in mA units                                     | 3000                 | Can be changed          |

| Source PDO 1                          | Second source PDO.                                                                  | 9 V @ 3A             | Can be changed          |

| Source PDO 2                          | Third source PDO.                                                                   | 15 V @ 3A            | Can be changed          |

| Source PDO 3                          | Fourth source PDO.                                                                  | 20 V @ 3A            | Can be changed          |

| Sink PDO                              |                                                                                     |                      |                         |

| Sink PDO 0                            | First sink PDO: Must be a 5 V fixed supply PDO.                                     | 5 V @ 0.9 A          | Current can be changed. |

| Sink PDO 1                            | Second sink PDO.                                                                    | 7 to 21 V @ 0.9<br>A | Can be changed.         |

| SCEDB Configuration: Source           | e Capabilities Extended Data Block                                                  |                      |                         |

| VID                                   | Vendor ID                                                                           | 0x04B4               | Can be changed          |

| PID                                            | Product ID                                                                                 | <as per<="" th=""><th>Can be changed</th></as> | Can be changed                            |

|------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------|

|                                                | 1 Toddet ID                                                                                | Project>                                       | our be changed                            |

| XID                                            | USB-IF assigned ID for the product.                                                        | 0                                              | Can be changed                            |

| FW Version                                     | Firmware version                                                                           | 1                                              | Can be changed                            |

| HW Version                                     | Hardware version                                                                           | 1                                              | Can be changed                            |

| Voltage regulation load step slew rate (mA/us) | Load variation allowed per us by the voltage regulator.                                    | 150                                            | Not allowed                               |

| Voltage regulation load step magnitude (%loC)  | Range of load variation allowed (%) allowed.                                               | 25                                             | Can be changed                            |

| Holdup Time (ms)                               | Time in ms for which the output voltage remains in holdup on interruption of input supply. | 0                                              | Can be changed                            |

| LPS compliant                                  | IEC power supply compliance status.                                                        | No                                             | Can be changed                            |

| PS1 compliant                                  | IEC power supply compliance status.                                                        | No                                             | Can be changed                            |

| PS2 compliant                                  | IEC power supply compliance status.                                                        | No                                             | Can be changed                            |

| Low touch current EPS                          | Touch current status bit.                                                                  | No                                             | Can be changed                            |

| Ground pin                                     | Whether Ground pin is supported.                                                           | Supported                                      | Can be changed                            |

| Touch temp                                     | Specifies IEC standard used to determine surface temperature.                              | Default: IEC<br>60950-1.                       | Can be changed                            |

| Source Inputs-External supplies                | External supply type.                                                                      | Constrained external supply                    | Can be changed                            |

| Source Inputs-Internal batteries               | Whether batteries are present.                                                             | No                                             | Can be changed                            |

| Hot swappable batteries                        | Number of hot swappable batteries.                                                         | 0                                              | Can be changed                            |

| Fixed batteries                                | Number of fixed batteries.                                                                 | 0                                              | Can be changed                            |

| Source PD Power                                | PD power supply capability in Watts.                                                       | 60                                             | Can be changed. Should match Source PDOs. |

| SKEDB Configuration: Sink C                    | Capabilities Extended Data Block                                                           |                                                |                                           |

| VID (0x)                                       | The 16-bit Vendor ID (VID) assigned to the Source's vendor by the USB-IF                   | 4B4                                            | Can't be changed                          |

| PID (0x)                                       | The 16-bit Product ID (PID) assigned by the Source's vendor                                | <as per<br="">Project&gt;</as>                 | Can't be changed                          |

| XID (0x)                                       | Value provided by the USB-IF to assign to product                                          | 00000000                                       | Can be changed                            |

| FW Version (0x)                                | Firmware version number                                                                    | 1                                              | Can be changed                            |

| HW Version (0x)                                | Hardware version number                                                                    | 1                                              | Can be changed                            |

| SKEDB Version (0x)                             | SKEDB Version                                                                              | 1                                              | Can't be changed                          |

| Load step slew rate (mA/us)                    | Indicates the Load Step Slew Rate and Magnitude that this Sink prefers                     | 150                                            | Can be changed                            |

| Percent overload                               | Percent overload in 10% increments. Values higher than 250 are clipped to 250%.            | 0                                              | Can be changed                            |

| Overload period (ms)                           | Overload period in ms.Value is stored in table as 20ms unit                                | 0                                              | Can be changed                            |

| Duty cycle                                     | Duty cycle in 5% increments                                                                | 0                                              | Can be changed                            |

| EMBEDDED IN TOMORROW         |                                                                                                                                                      |                    |                                          |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------|

| VBUS Voltage droop tolerance | Can tolerate VBUS Voltage droop                                                                                                                      | No                 | Can be changed                           |

| LPS Compliant                | Whether sink is LPS compliant                                                                                                                        | No                 | Can be changed                           |

| PS1 Compliant                | Whether sink is PS1 compliant                                                                                                                        | No                 | Can be changed                           |

| PS2 Compliant                | Whether sink is PS2 compliant                                                                                                                        | No                 | Can be changed                           |

| Touch Temp                   | The IEC standard used to determine the surface temperature of the Sink's enclosure                                                                   | Default            | Can be changed                           |

| Hot swappable batteries      | Number of hot swappable batteries (04)                                                                                                               | 0                  | Can be changed                           |

| Fixed batteries              | Number of fixed batteries (04)                                                                                                                       | 0                  | Can be changed                           |

| PPS charging supported       | Ability of Sink to use a PPS Source for fast charging                                                                                                | No                 | Can be changed                           |

| VBUS powered                 | Ability of Sink to be sourced by Vbus                                                                                                                | Yes                | Can be changed                           |

| Mains powered                | Ability of Sink to be sourced by an external mains power supply                                                                                      | No                 | Can be changed                           |

| Battery powered              | Ability of Sink to be sourced by a battery                                                                                                           | Yes                | Can be changed                           |

| Unlimited battery powered    | Ability of Sink to be sourced by a battery with essentially infinite energy (e.g. a car battery)                                                     | No                 | Can be changed                           |

| Sink minimum PDP             | The Minimum PDP required by the Sink to operate without consuming any power from its Battery(s) should it have one.                                  | 5                  | Can be changed                           |

| Sink operational PDP         | The PDP the Sink requires to operate normally. For Sinks with a Battery, it is the PDP Rating of the charger supplied with it or recommended for it. | 15                 | Can be changed                           |

| Sink maximum PDP             | The Maximum PDP the Sink can consume to operate and charge its Battery(s) should it have one.                                                        | 20                 | Can be changed                           |

| Peak Current <sup>1</sup>    |                                                                                                                                                      |                    |                                          |

| Percentage overload (%)      | Percentage of overload allowed.                                                                                                                      | 0                  | Can be changed                           |

| Overload period (ms)         | Period in ms of the rolling average time window for overloading.                                                                                     | 0                  | Can be changed                           |

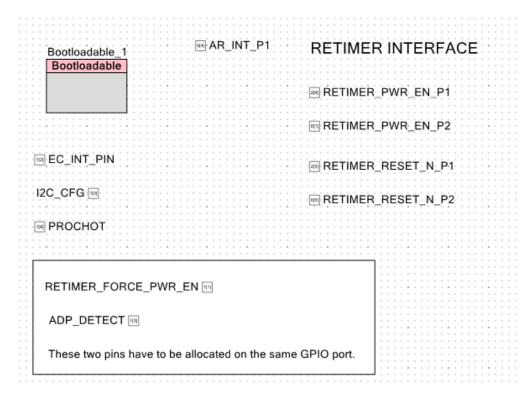

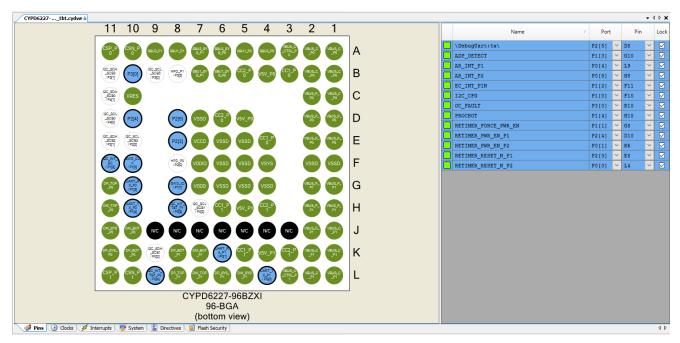

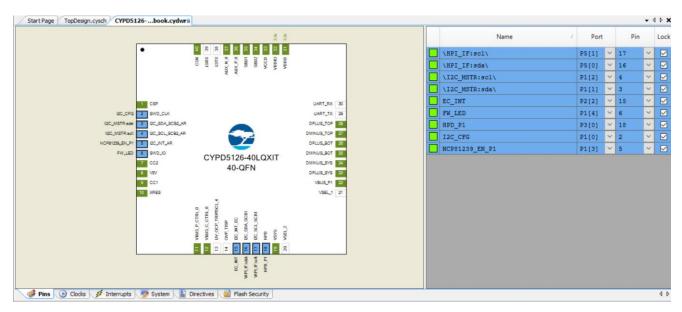

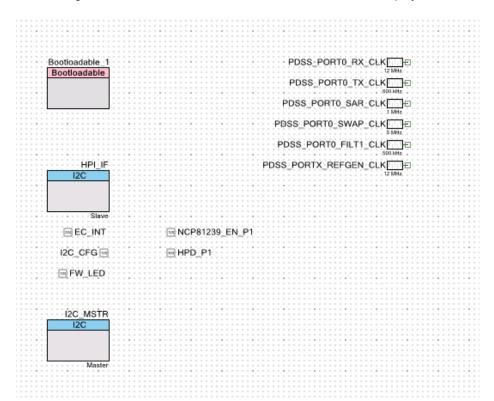

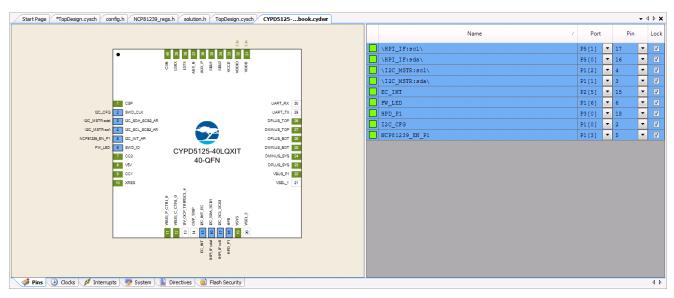

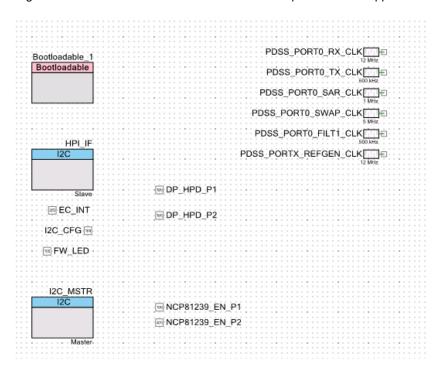

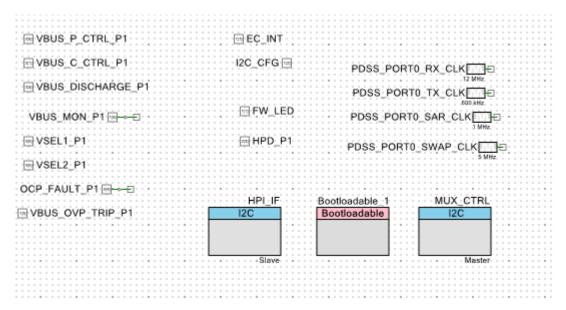

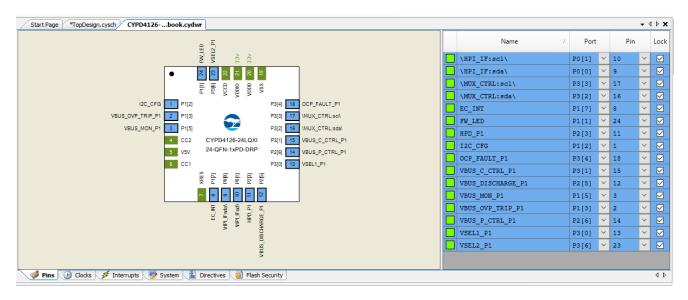

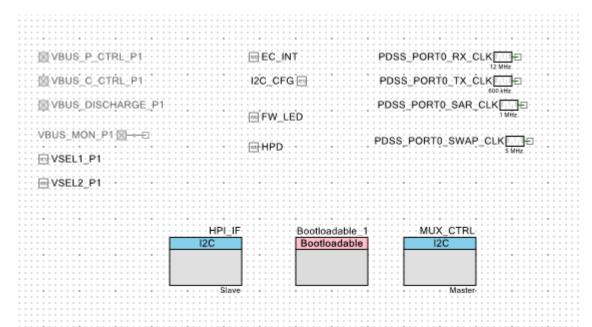

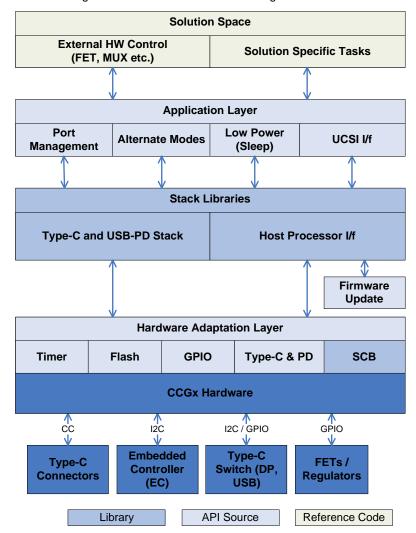

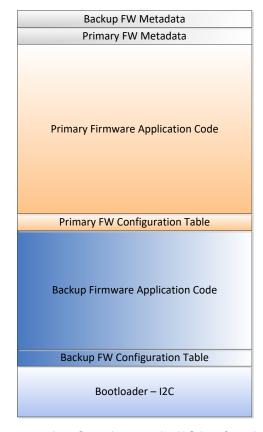

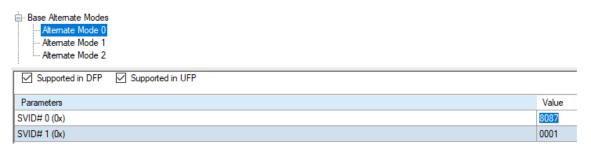

| Duty cycle (%)               | Percentage of time for which overloading persists within the rolling window.                                                                         | 0                  | Can be changed                           |