## **Test Report for ECC**

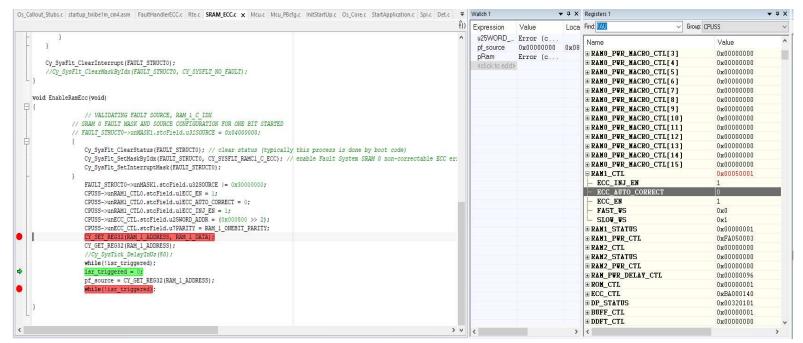

Test case 1: Writing 0x5A5A5A5A into address of SRAM1 0x08010500 with correct parity when ECC is enabled.

Output: No fault is reported and ISR is not triggered. The above-mentioned address has the value that is written.

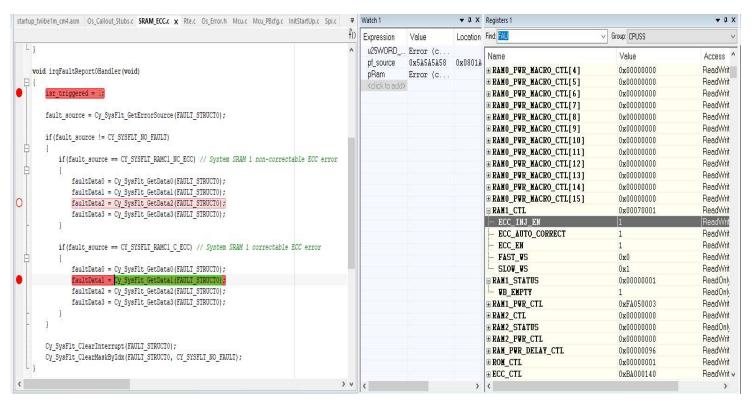

Test case 2: Writing 0x5A5A5A5A into address of SRAM1 0x08010500 with one-bit parity error when ECC error injection is enabled.

Auto correct is enabled but memory is still showing error injected data.

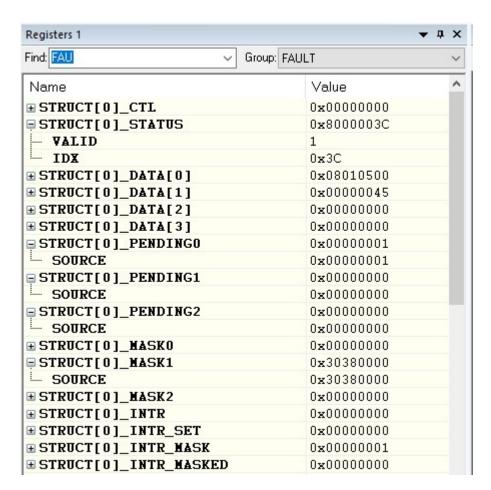

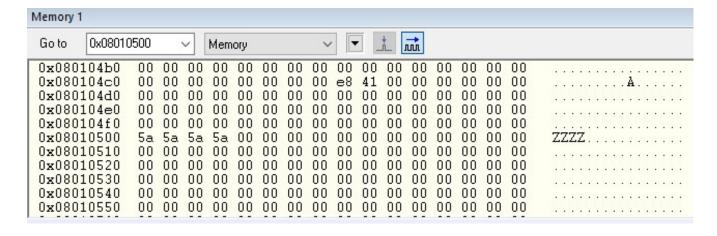

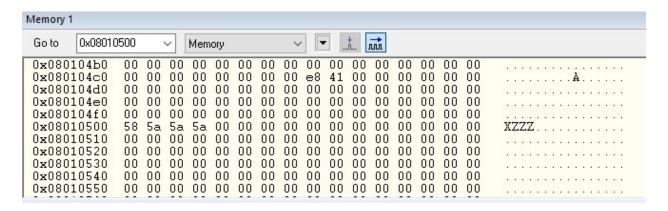

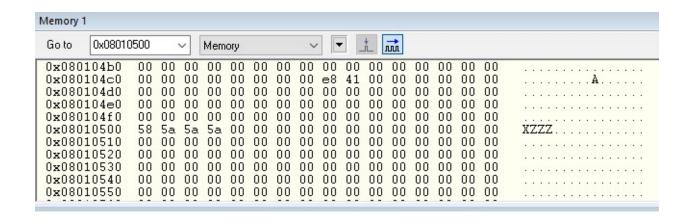

## Test case 3: Writing 0x5A5A5A5A into address of SRAM1 0x08010500 with Two-bit parity error when ECC error injection is enabled.(non-correctable)

| Go to  | 0x08010 | 500 | •   | ~] [ | Mem | ory |     |     | ~  | -  |    |    | vii |     |     |    |     |          |

|--------|---------|-----|-----|------|-----|-----|-----|-----|----|----|----|----|-----|-----|-----|----|-----|----------|

| )x0801 | 04Ь0    | 00  | 00  | 00   | 00  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 00  |          |

| x0801  | 04c0    | 0.0 | 0.0 | 0.0  | 0.0 | 0.0 | 0.0 | 0.0 | 00 | e8 | 41 | 00 | 0.0 | 0.0 | 0.0 | 00 | 00  | <b>A</b> |

| x0801  | 04d0    | 00  | 0.0 | 00   | 00  | 0.0 | 0.0 | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 00  |          |

| x0801  | 04e0    | 0.0 | 00  | 00   | 00  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 00  |          |

| x0801  | 04f0    | 00  | 00  | 00   | 00  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 00  |          |

| x0801  | 0500    | 1a  | 5a  | 5a   | 5a  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 0.0 | .ZZZ     |

| x0801  | 0510    | 00  | 00  | 00   | 00  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 00  |          |

| x0801  | 0520    | 00  | 00  | 00   | 00  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 0.0 |          |

| x0801  | 0530    | 00  | 00  | 00   | 00  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 0.0 |          |

| x0801  | 0540    | 0.0 | 00  | 00   | 00  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 00  |          |

| x0801  | 0550    | 00  | 00  | 00   | 00  | 00  | 00  | 00  | 00 | 00 | 00 | 00 | 00  | 00  | 00  | 00 | 00  |          |

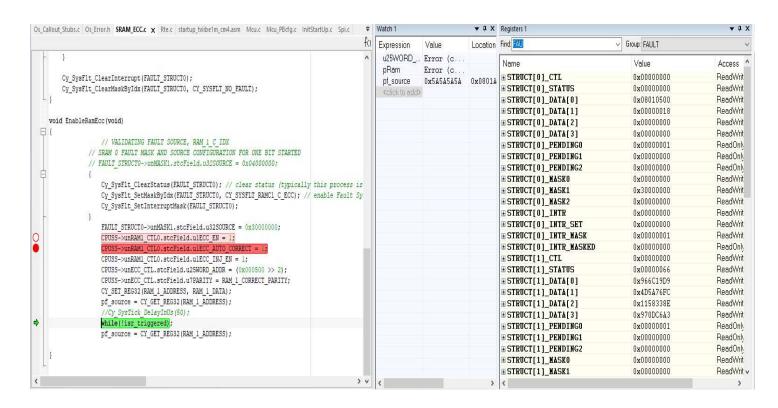

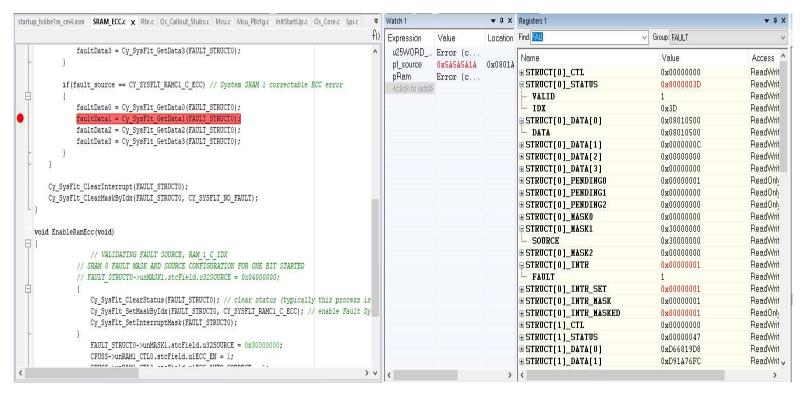

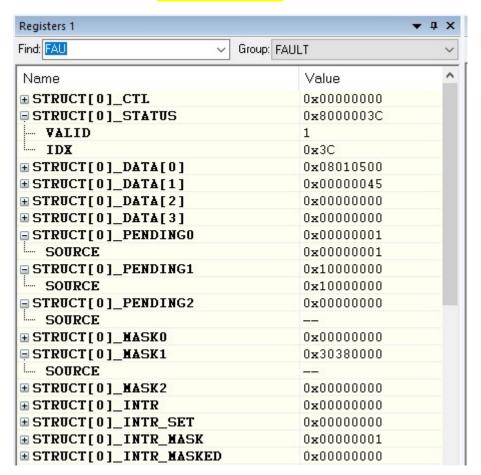

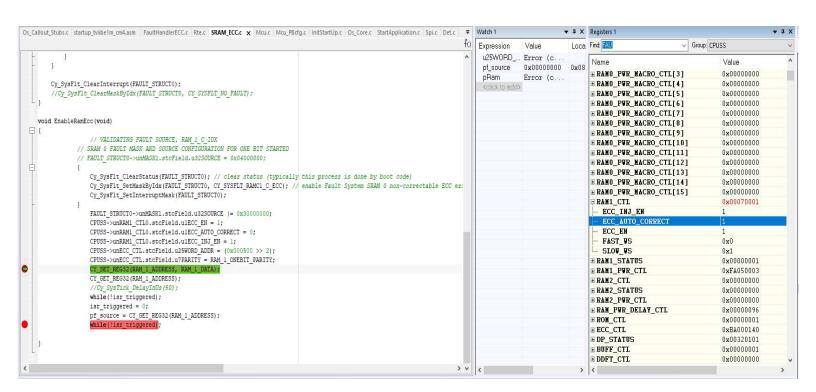

Test case 4: Writing 0x5A5A5A5A into address of SRAM1 0x08010500 with one-bit parity error when ECC error injection is enabled and trying read the data from same memory twice with AUTO CORRECT disabled.

```

void EnableRamEcc(void)

₽ {

// VALIDATING FAULT SOURCE, RAM 1 C IDX

// SRAM O FAULT MASK AND SOURCE CONFIGURATION FOR ONE BIT STARTED

// FAULT_STRUCTO->unMASK1.stcField.u32SOURCE = 0x04000000;

Cy_SysFlt_ClearStatus(FAULT_STRUCTO); // clear status (typically this process is done by boot code)

Cy_SysFit_SetMaskByIdx(FAULT_STRUCTO, CY_SYSFLT_RAMC1_C_ECC); // enable Fault System SRAM 0 non-correctable ECC er:

Cy_SysFlt_SetInterruptMask(FAULT_STRUCT0);

FAULT_STRUCTO->unMASK1.stcField.u32SOURCE |= 0x300000000;

CPUSS->unRAM1_CTL0.stcField.ulECC_EN = 1;

CPUSS->unRAM1_CTL0.stcField.ulECC_AUTO_CORRECT = 0;

CPUSS->unRAM1_CTL0.stcField.ulECC_INJ_EN = 1;

CPUSS->unECC_CTL.stcField.u25WORD_ADDR = (0x000500 >> 2);

CPUSS->unECC_CTL.stcField.u7PARITY = RAM_1_ONEBIT_PARITY;

CY_SET_REG32 (RAM_1_ADDRESS, RAM_1_DATA);

CY_GET_REG32 (RAM_1_ADDRESS);

//Cy_SysTick_DelayInUs(50);

while(!isr_triggered);

isr_triggered = 0;

pf_source = CY_GET_REG32(RAM_1_ADDRESS);

while(!isr_triggered);

```

| RAM1_CTL                   | 0x00050001 |  |  |  |  |

|----------------------------|------------|--|--|--|--|

| ECC_INJ_EN                 | 1          |  |  |  |  |

| ECC_AUTO_CORRECT           | 0          |  |  |  |  |

| - ECC_EN                   | 1          |  |  |  |  |

| FAST_VS                    | 0x0        |  |  |  |  |

| - SLOU_US                  | 0x1        |  |  |  |  |

| □ RAN1_STATUS              | 0x0000001  |  |  |  |  |

| - VB_EMPTY                 | 1          |  |  |  |  |

| <b>⊞ RAM1_PWR_CTL</b>      | 0xFA050003 |  |  |  |  |

| RAM2_CTL                   | 0x0000000  |  |  |  |  |

| <b>⊞ RAM2_STATUS</b>       | 0x0000000  |  |  |  |  |

| RAM2_PWR_CTL               | 0x0000000  |  |  |  |  |

| <b>⊞ RAM_PWR_DELAY_CTL</b> | 0x00000096 |  |  |  |  |

| ROM_CTL                    | 0x0000001  |  |  |  |  |

| □ ECC_CTL                  | 0xBA000140 |  |  |  |  |

| PARITY                     | 0x5D       |  |  |  |  |

| - WORD_ADDR                | 0x000140   |  |  |  |  |

During the second read operation, the fault is not triggered immediately, but getting updated to Pending Register 1.

Test Case 5: Writing 0x5A5A5A5A into address of SRAM1 0x08010500 with one-bit parity error when ECC error injection is enabled and trying read the data from same memory twice.

Note: During First read AUTO\_CORRECT is enabled and second read AUTO\_CORRECT is disabled.

Observations: During first time read fault is getting serviced and memory is not updated with correct data.

Observations: During second time read, fault is neither serviced nor reported to fault structure as a pending source.