# Introduction to Low Power Modes in PSoC 6

Rakshith M B Applications Engineer 30th July, 2020

## **Demo – Simple Low Power Mode**

### **Agenda**

- Low Power MCU Systems

- Low Power Features in PSoC 6

- System and CPU power modes

- CPU Power Modes

- System Power Modes

- > Transitioning between Power Modes

- Power Mode Transition Callbacks

- Demo

- Power Reduction Techniques

- Backup Domain

### **Low Power MCU Systems**

- Small

- Wireless

- Larger feature set

- Higher battery backup

- Lesser cost

- Security

#### Low Power Features in PSoC 6

- Designed for low power

- No significant sacrifice in performance

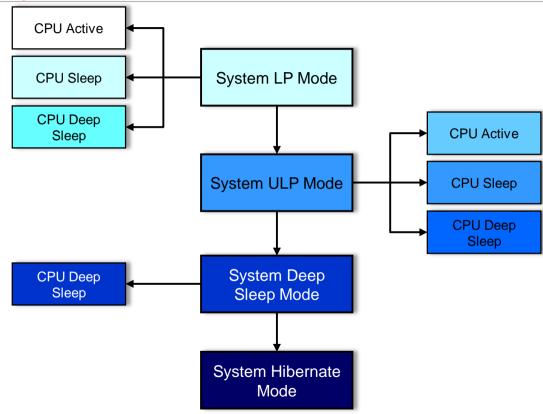

- 7 power modes 4 system and 3 CPU power modes

- MCU Active Power 22 uA / MHz

- Low operational voltage support (1.1 V or 0.9 V)

- Low Power Assistant

- SysPm PDL, HAL driver support

#### **CPU Power modes**

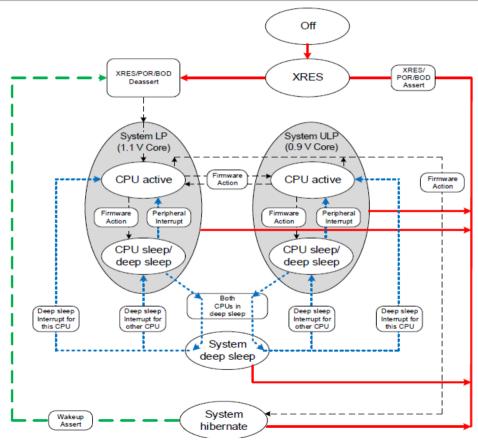

### **System Power modes**

Standard ARM-defined power modes

Additional low power modes supported by PSoC 6

- Different CPU power modes

- CPU Active

- CPU Sleep

- CPU Deep Sleep

- Specific to the CPU and entered separately > for each CPU

- Retains program state

- Based on WFI and WFE instructions

- > Implementation is vendor specific

- Different System power modes

- System Low Power

- System Ultra Low Power

- System Deep Sleep

- System Hibernate

- Affects the whole system

- All CPU power modes are available in both System Low Power (LP) and System Ultra Low Power (ULP) modes

# **CPU Power Modes**

|                        | Active                                                                        | Sleep                                                                                                           | Deep Sleep                                                                                                                                                                |

|------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code<br>Execution      | CPU executes code                                                             | <ul> <li>CPU executes WFI/WFE instruction with Deep Sleep disabled</li> <li>CPU halts code execution</li> </ul> | <ul> <li>CPU executes WFI/WFE instruction with Deep Sleep enabled</li> <li>CPU halts code execution</li> <li>Requests device to go into System Deep Sleep mode</li> </ul> |

| Resources<br>Available | <ul><li>All peripherals are<br/>available</li><li>Memory is powered</li></ul> | <ul><li>All peripherals are available</li><li>CPU clock turned off</li></ul>                                    | <ul><li>All peripherals are available</li><li>CPU clock turned off</li></ul>                                                                                              |

| Wakeup<br>Source       | CPU enters Active mode<br>on reset or wakeup                                  | Any peripheral interrupt will<br>transition CPU to Active<br>mode                                               | Any peripheral interrupt<br>will transition CPU to<br>Active mode                                                                                                         |

# System Power Modes

### **Overview of System Power Modes**

|                        | System LP Mode                                                                                                                                                | System ULP Mode                                                                                                                       | System Deep Sleep                                                                                                                                                                                                                                                                                 | System Hibernate                                                                                                                                                                                                                                                                                                                                 |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Features               | <ul> <li>Default operating mode</li> <li>Maximum system         performance</li> <li>Maximum clock         frequencies</li> <li>1.1 V core voltage</li> </ul> | Restricted system performance     Limited clock frequencies     0.9 V core voltage                                                    | <ul> <li>Achievable when both CM4 and CM0+ enters CPU Deep Sleep</li> <li>LP and ULP Regulators turned off. Deep Sleep regulators used.</li> <li>Buck Regulator can be used</li> <li>On wakeup only the woken up CPU enters Active mode.</li> <li>System returns to LP or ULP</li> </ul>          | <ul> <li>Lowest power mode of the device</li> <li>LP/ULP and Deep Sleep regulators are off</li> <li>Brown out detection is not available.</li> <li>Supply should be stable for at least 250 us before entering Hibernate mode</li> <li>GPIO states are frozen</li> <li>Device resets on wakeup -&gt; Reset reason is Hibernate Wakeup</li> </ul> |  |

| Resources<br>Available | All resources are<br>available                                                                                                                                | HF Clocks are restricted to 50 MHz Peripheral and slow clocks restricted to 25 MHz No Flash write actions All resources are available | <ul> <li>HF Clocks are disabled.</li> <li>High speed peripherals not available.</li> <li>Low speed clocks and peripherals available.</li> <li>Externally clocked peripheral (Deep Sleep capable SPI/I2C slave).</li> <li>SRAM blocks can be retained.</li> <li>LPComp, WDT, MCWDT, RTC</li> </ul> | <ul> <li>All peripherals and clocks are off</li> <li>PWR_HIBERNATE and         PWR_HIB_DATA registers are         retained.</li> <li>ILO</li> <li>LPComp, WDT, RTC</li> </ul>                                                                                                                                                                    |  |

| Wakeup<br>Source       | Any interrupt to CPU                                                                                                                                          | Any interrupt to CPU                                                                                                                  | GPIO LPComp SCB CTBm WDT RTC alarm                                                                                                                                                                                                                                                                | Wakeup pins     LPComp (requires externally generated voltages for wakeup)     WDT     RTC alarm                                                                                                                                                                                                                                                 |  |

#### An Example...

1

#### **System LP**

- User active

- Max performance for continuous tracking

- CPU in Active mode

2

#### System ULP

- User in rest for more than 15 min

- CPU in Sleep mode

3

#### System Deep Sleep

- Night

- User in rest for more than an hour

4

#### **System Hibernate**

- Battery Low

- Save tracking data

### **Movement Tracking Watch**

|   | Power - Parameters |                               |                           |  |  |

|---|--------------------|-------------------------------|---------------------------|--|--|

|   | Ent                | Enter filter text             |                           |  |  |

|   | Na                 | me                            | ue                        |  |  |

|   | •                  | Documentation                 |                           |  |  |

|   |                    | ? SysPm API Reference         | Open SysPm Documentation  |  |  |

|   | •                  | General                       |                           |  |  |

|   |                    | ③ System Active Power Mode    | LP                        |  |  |

|   |                    | ? Core Regulator              | Minimum Current Buck      |  |  |

|   |                    | ? Enable External PMIC Output |                           |  |  |

|   |                    | ② vBackup Source              | VDDD                      |  |  |

|   | •                  | RTOS                          |                           |  |  |

|   |                    | ? System Idle Power Mode      | System Deep Sleep         |  |  |

|   |                    | ? Deep Sleep Latency (ms)     | 0                         |  |  |

|   | •                  | Operating Conditions          |                           |  |  |

| - |                    | ③ VDDA Voltage (mV)           | 3300                      |  |  |

|   |                    | ③ VDDD Voltage (mV)           | 3300                      |  |  |

|   |                    | ? VBACKUP Voltage (mV)        | 3300                      |  |  |

|   |                    | ② VDD_NS Voltage (mV)         | 3300                      |  |  |

|   |                    | ② VDDIO0 Voltage (mV)         | 3300                      |  |  |

|   |                    | ③ VDDIO1 Voltage (mV)         | 3300                      |  |  |

|   | •                  | Wakeup Pins                   |                           |  |  |

|   |                    | ? Hibernate Wakeup (0)        | <unassigned></unassigned> |  |  |

|   |                    | ? Hibernate Wakeup (1)        | <unassigned></unassigned> |  |  |

|   |                    |                               |                           |  |  |

# Transitioning between Power Modes

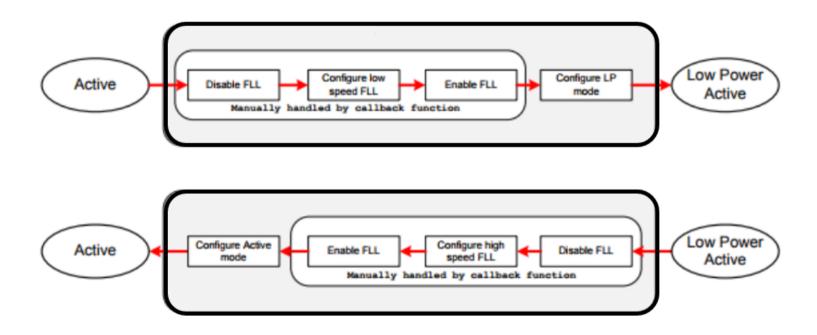

#### **Transitioning to System LP Mode**

Configure the core regulator to 1.1 V

Wait 9 us to allow the core voltage to stabilize

Increase clock frequencies up to max frequencies if needed

To transition to low power -

cyhal\_syspm\_set\_system\_state(CYHAL\_SYSPM\_SYSTEM\_NORMAL);

- API takes care of setting the right core regulator voltage.

- Returns success of the transition is successful.

To change clock frequency -

cyhal\_clock\_set\_frequency()

> The clocks need to be configured by the application

<sup>\*</sup>Blue outline indicates that the step needs to be performed by the application.

#### **Transitioning to System ULP Mode**

Slow or disable peripherals

Decrease clock frequencies below ULP limitations

Set appropriate wait state values for the flash

Configure the core regulator to 0.9 V

To change clock frequency –

cyhal\_clock\_set\_frequency()

The clocks need to be configured by the application

To transition to low power -

cyhal\_syspm\_set\_system\_state(CYHAL\_SYSPM\_SYSTEM\_LOW);

- API takes care of setting the appropriate wait states and core regulator voltage.

- Returns success of the transition is successful.

<sup>\*</sup>Blue outline indicates that the step needs to be performed by the application.

### **Transitioning to CPU Sleep Mode**

Clear all pending interrupts

Ensure that SLEEPDEEP bit of SCR register of CPU is cleared

Execute WFI/WFE instruction

To transition to low power -

cyhal\_syspm\_sleep();

- HAL API takes care of clearing the SLEEPDEEP bit and executing the WFI/WFE instruction.

- Returns success of the transition is successful.

#### **Transitioning to System Deep Sleep Mode**

Clear all pending interrupts

Clear the HIBERNATE bit of the PWR\_HIBERNATE register

Set the SLEEPDEEP bit of the SCR register

Execute WFI/WFE instruction

\*Green outline indicates the steps that are different from CPU Sleep transition

To transition to low power -

cyhal\_syspm\_deepsleep();

- API takes care of setting the appropriate wait bits and executing ARM instructions.

- > Returns success of the transition is successful.

- Application must ensure that both CPUs call the API to enter System Deep Sleep.

#### **Transitioning to System Hibernate Mode**

Set the PWR\_HIB\_DATA register

Set the TOKEN bits and UNLOCK bits of the PWR\_HIBERNATE register

Configure wakeup source

Set the HIBERNATE bit of the PWR\_HIBERNATE register

\*Blue outline indicates that the step needs to be performed by the application.

To transition to low power -

cyhal syspm hibernate(<wakeup source>);

- HAL API takes care of the entire process other than setting PWR\_HIB\_DATA.

- Returns success of the transition is successful.

- Application specific data can be retained in the PWR HIB DATA register if needed by the application.

# Power Mode Transition Callbacks

#### **Callback Functions**

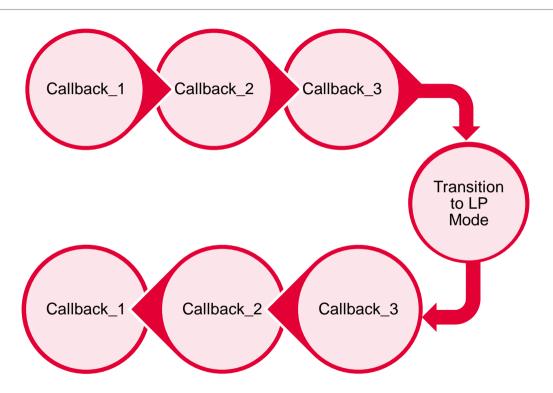

#### **Callback Sequence**

- Generally each peripheral gets a callback

- Sequence based on order of registration

- Global resource callbacks should be registered last

- Should not be modified after registration

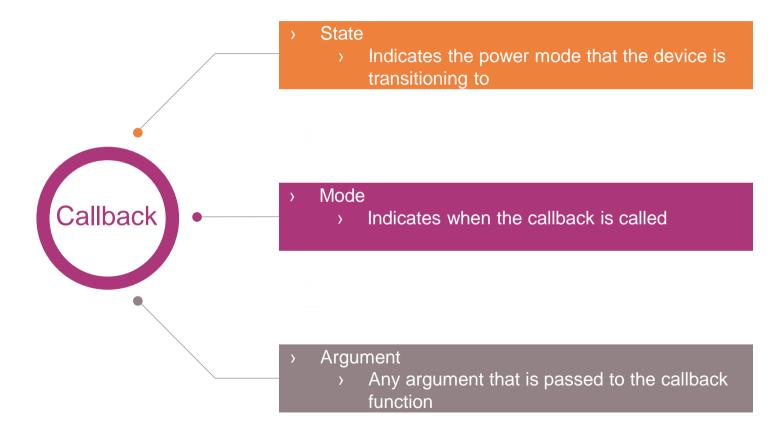

#### **Callback Parameters**

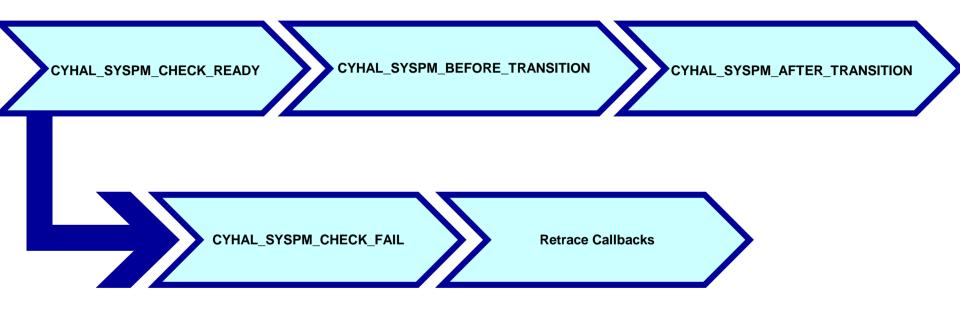

#### **Callback Execution Flow**

#### Callback Usage

#### Callback Declaration

```

/* Callback declaration for Power Modes */

cyhal syspm callback data t pwm callback = {pwm power callback,

/* Callback function */

CYHAL SYSPM CALLBACK STATE ALL, /* Power States supported */

CYHAL SYSPM CHECK FAIL,

/* Modes to ignore */

/* Callback Argument */

NULL,

NULL);

/* For internal use */

cyhal syspm callback data t clk callback = {clk power callback,

/* Callback function */

CYHAL SYSPM CALLBACK STATE ALL, /* Power States supported */

CYHAL SYSPM_CHECK_READY

/* Modes to ignore */

CYHAL SYSPM CHECK FAIL,

NULL,

/* Callback Argument */

NULL);

/* For internal use */

```

#### Callback Registration

```

/* Power Management Callback registration */

cyhal_syspm_register_callback(&clk_callback);

cyhal_syspm_register_callback(&pwm_callback);

```

# Demo

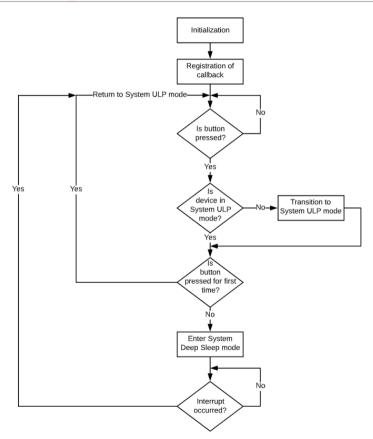

### **Demo – System Deep Sleep Mode**

# Power Reduction Techniques

#### **Disable Unnecessary Resources**

- GPIO pins

- Change GPIO pin state to High Impedance

- External Components

- Powering through PSoC and disabling it in firmware

- Disable peripherals

- Disable Debug Mode

- Disable unused SRAM pages and/or banks

- Each page is generally 32 KB

- Use of custom linker scripts

- Disable UDBs (if present)

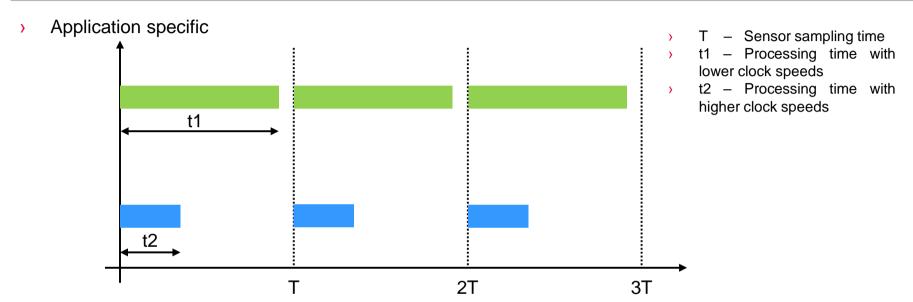

#### **Clock Speeds**

- Use appropriate clocks for peripherals

- Do not use 1 MHz clock for a timer with 1 second period

#### **Other Power Reduction Techniques**

- Use DMA for data transfer

- Avoid blocking functions -> poll for interrupt based events

- Select the SCB that has Deep Sleep capability

- Select GPIO with wakeup capability

- Select appropriate regulator and core voltage

### **Factors affecting the current measured**

- Multimeter accuracy

- Multimeter shunt resistor

- Current measurement guidelines of the Kit

- 7. What is the Jumper on board for?

The jumper **J8** can be used to measure current of PSoC 6 MCU device without the need to desolder any component from the board. An ammeter can be connected across this jumper to measure the current consumed by the PSoC 6 MCU device. Remove the Jumper on **J8**, connect an ammeter (+ve terminal of ammeter to Pin 2), and power the kit though USB connector **J10**.

Note: Please remove resistor R4 which causes a leakage of 4 μA on VBACKUP domain that is connected to VTARG

Datasheet current measurement conditions

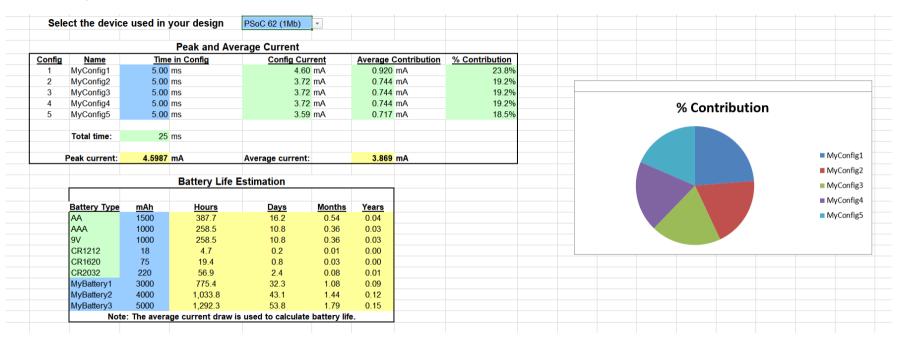

### **Approximating Power Consumption – PSoC6 Power Calculator**

#### Instructions

#### Instructions

- 1. Select/enter values for as many Config worksheets as wanted.

- 2. In the Battery Life worksheet, enter the amount of time (in miliseconds) spent in each Config.

- 3. In the Battery Life worksheet, enter values for the type and/or capacity of your batteries.

- 4. The estimates will be shown in the tables on the Battery Life worksheet.

#### **Cell Color Coding**

- =Cell in which the values are fixed or automatically generated. Do not edit.

- =Cell in which data can be entered or selected by the user.

- =Total calculated value. Do not edit.

- =Cell used for power calculation. Do not edit.

- =Cell selection needs to be reviewed.

#### Worksheets

These worksheets are linked together and reference each other. Do not delete any worksheets. The Battery Life worksheet has cells where you enter the amount of time spent in each configuration. Set the time to zero instead of deleting a worksheet.

#### **Battery Life**

This tab contains the totals from all 5 of the Config tabs, and it uses these values to calculate and estimated battery life based upon the current draw and the amount of time spent in each config mode.

#### Config(1 to 5)

These worksheets calculate the current for a specific configuration. The spreadhseet supports five different configurations. Select or enter the configuration values for each of the items on the config worksheet. The current consumption for that configuration is displayed at the bottom. You can give the configuration a name at the top to make it easier to identify on the Battery Life worksheet.

### **Approximating Power Consumption – PSoC6 Power Calculator**

#### Filling in details

|                        | Settings     |       | Current |    | <u>Notes</u>                                                                   |

|------------------------|--------------|-------|---------|----|--------------------------------------------------------------------------------|

|                        |              |       |         |    | System                                                                         |

| Power Settings         |              |       |         |    | - Cystom                                                                       |

| PSoC VDDD Voltage      | 3.3          | Volts |         |    | Set the VDDD Voltage                                                           |

| Power Mode Regulator   | BUCK         |       |         |    | Select the regulator type                                                      |

| Regulator Voltage Core | 1.1          | Volts |         |    | Select the regulator core voltage. This affects the System Power Mode options. |

| System Power Mode      | System LP    |       |         |    | Select the PSoC 6 System Power Mode. This affects the CPU power mode options   |

| CM0+ CPU Power Mode    | CPU Sleep    |       |         |    | Select the CM0+ CPU Power Mode                                                 |

| CM4 CPU Power Mode     | CPU Sleep    |       |         |    | Select the CM4 CPU Power Mode                                                  |

| Clocks                 |              |       |         |    |                                                                                |

| PLL / FLL              |              |       |         |    |                                                                                |

| <b>✓</b> FLL           | 100          | MHz   | 540.000 | μΑ | Enter the FLL frequency                                                        |

| PLL0                   |              |       | 0.000   | μΑ | Enter the PLL0 Frequency                                                       |

| - Feedback             |              |       |         |    | Enter the PLL0 Feedback                                                        |

| - Reference            |              |       |         |    | Enter the PLL0 Reference                                                       |

| PLL1                   |              |       | 0.000   | μΑ | Enter the PLL1 Frequency                                                       |

| - Feedback             |              |       |         |    | Enter the PLL1 Feedback                                                        |

| - Reference            |              |       |         |    | Enter the PLL1 Reference                                                       |

| High Frequency Clocks  |              |       |         |    |                                                                                |

| Clk_HF0                | Divided by 1 | FLL   |         |    | Enter the High Frequency Clock 0 divider and source                            |

| Clk_HF1                |              |       |         |    | Enter the High Frequency Clock 1 divider and source                            |

| ☐ Clk_HF2              |              |       | 0.000   | μĀ | Enter the High Frequency Clock 2 divider and source                            |

| ☐ Clk_HF3              |              |       |         |    | Enter the High Frequency Clock 3 divider and source                            |

| ☐ Clk_HF4              |              |       |         |    | Enter the High Frequency Clock 4 divider and source                            |

| Clk_HF5                |              |       |         |    | Enter the High Frequency Clock 5 divider and source                            |

#### **Approximating Power Consumption – PSoC6 Power Calculator**

#### Summary

# Backup Domain

#### **Backup Domain**

- Always on functionality

- Automatic backup power switching ->  $V_{DDBAK} = V_{DDD} | V_{BACKUP}$

- Reset only when power is completely removed or Backup Domain is reset through firmware

- > Fully featured RTC with configurable alarm

- 32 kHz WCO

- > Built-in supercapacitor charger

- External PMIC control

- 32-byte backup registers

- BACKUP\_BREG0 to BACKUP\_BREG15

- Used to store specific device related information

#### Resources

- > PSoC® 6 MCU Architecture TRM

- PSoC 6 MCU Low-Power Modes and Power Reduction Techniques

- > PSoC 6 Power Calculator.xlsx

- HAL API Reference Guide

- ModusToolbox® Software Environment

- Code Examples: Github repository

Part of your life. Part of tomorrow.